MIPI C-PHY / D-PHY サブシステムを解き明かす

トレードオフ、課題、そして採用

About the Author:

Ashraf Takla

President & CEO, Mixel, Inc.

初版発行:2018年4月、更新:2022年3月

MIPI® C-PHYSM は、興奮と不安が入り混じる中、2014 年 10 月に登場しました。この新しい C-PHYを MIPI D-PHYSM および M-PHY® と比較するとどうなるだろう? C-PHY の違いとは何だろう? また、ハイブリッドサブシステムで共存できるようなD-PHY との互換性はあるだろうか?

数年が経過した現在、それらの答えは明らかになりました。

本稿では、これらそれぞれの答えを説明し、D-PHY・C-PHY 双方のアーキテクチャの概要を示し、類似点と相違点に着目しながら各 PHY の長所と短所を特定し、C-PHY実装時に遭遇するいくつかの課題について考察を提供します。最後に、Mixel® の C-PHY/D-PHY コンボ IP の革新的な実装、複数ソースからのシリコン実績、ユースケースを紹介し、市場でのC-PHY/D-PHY コンボソリューションの採用を考察します。

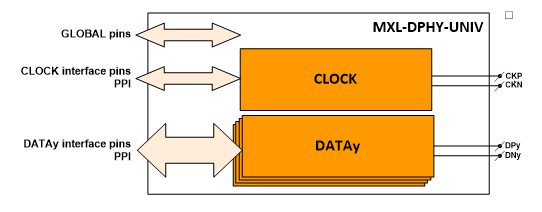

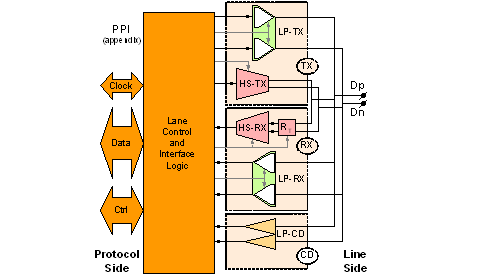

まず、D-PHYについて詳しく見てみましょう。D-PHY は 2009 年から存在しており、そのため理解が深まり広く導入されています。D-PHY は、1 つのクロックレーンと複数のデータレーンを使用するシンプルなソースシンクロナスPHY です。4データレーンD-PHY のブロックダイアグラムを図1に示し、各レーンの詳細を図2に示します。D-PHY は 10 年近く市場に投入されているため、独自の機能とユースケースをカバーする豊富な文献が存在します(1)。

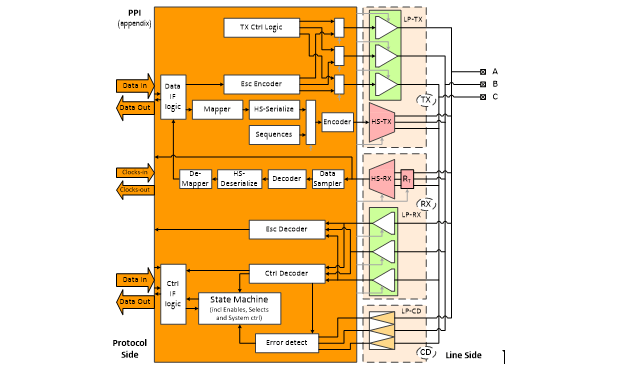

対照的に、C-PHY はより新しく複雑な PHY です。3 つの信号(トリオ)で動作し、クロックがデータに埋め込まれているため、別途のクロックレーンが不要になります。C-PHY のブロック図を図3に示します。

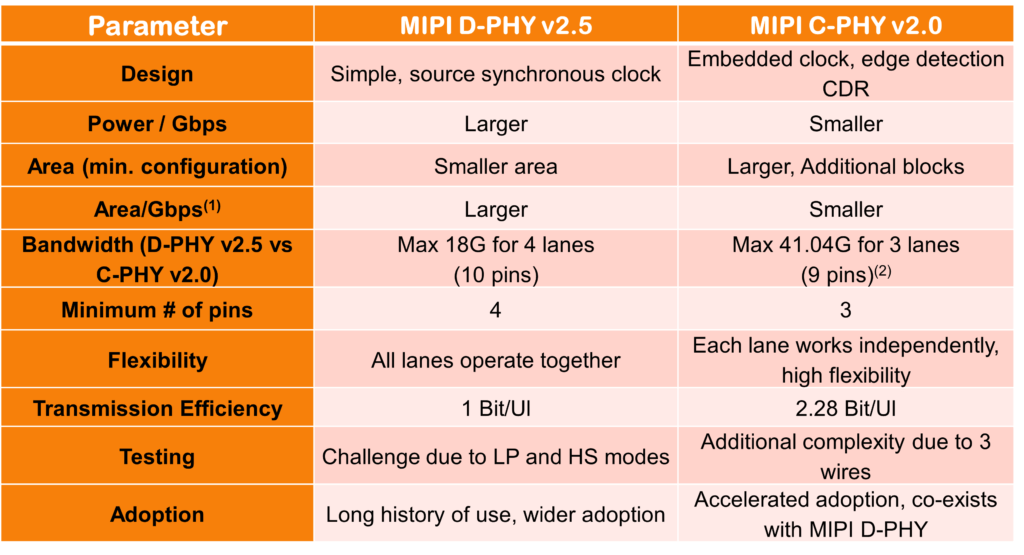

Table 1 D-PHYとC-PHYの比較

Notes: (1) 4 D-PHYレーン vs. 3 MIPI C-PHYトリオ

(2) エンコーディングによる高い帯域

D-PHY はエンコードを使用しないのに対し、C-PHY はエンコードされたデータを使用して 1UIに16/7 ≈ 2.28 ビット/シンボルを詰め込みます。 そのため、C-PHY は、同じ遷移レートまたはシンボルレートで動作しながら、D-PHYと比較してより高いデータレートを実現できます。

一見すると、C-PHYの仕組み、および可能であるであろうC-PHY・D-PHYコンボは神秘的に見えるかもしれません。C-PHYシグナリングはマルチレベルですが、レシーバーはそのマルチレベル間の違いを検出する必要はありません。 どうしてそんなことが可能なのでしょうか? C-PHY と D-PHY は、明確な違いがあるにもかかわらず、共存するだけでなく、効率的に1つの IP に統合するにはどうすればよいでしょうか? D-PHYは差動シグナリングを使用するのに対し、C-PHY はトリオを使用します。 それらが共に動作することは可能でしょうか? すべてのD-PHY構成要素を重複せずに使用して、C-PHY・D-PHYコンボを効率的に実装するにはどうすればよいでしょうか? シンボルあたりのデータ ビット数の 16/7 という比率はどこから来たのでしょうか? 非常に多くの質問が出てきます!

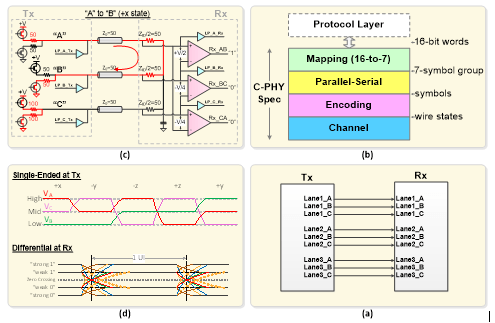

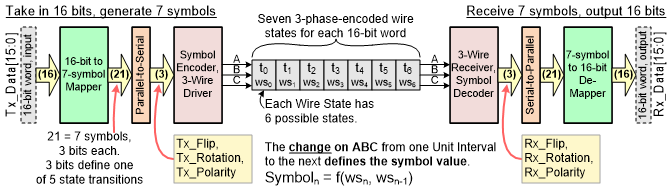

まず C-PHY をわかりやすく理解することで、これらの質問に答えてみましょう。 簡単な事ではありませんが。 以下の図4に、C-PHYの概要を示します。 図4(a) のブロック図は、3レーンC-PHYのTXとRX がどのように接続されているかを示しています。 図4(b) は、C-PHYサブシステムのさまざまなサブブロック、つまりマッピング、パラレル/シリアル機能、エンコーディング、およびチャネルを示しています。 図4(c) は TXとRXの間の相互作用のより詳細な図であり、図4(d) はC-PHY信号レベルを示しています。

C-PHYレーンは、上の図4(c) に示すように、A、BおよびCのトリオで構成されます。 C-PHYのレシーバは3つの差動 RXで構成されており、それぞれが3つの信号のうちの2つ、(A-B)、(B-C)、および (C-A) の差を調べます。

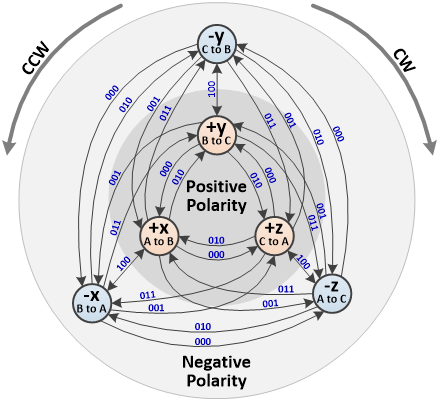

C-PHYのエンコーダは、(i)シンボルごとに少なくとも1つのエッジ・遷移があること、(ii) 3つすべてのRXの差動入力が非ゼロであること、および (iii)3つすべての信号のコモンモードが一定であること。 上記の項目 (ii) および (iii) は、単一のユニットインターバル (UI) 中のTX信号の組み合わせを高、中、低に制限し、3つの信号それぞれの電圧レベルを異なる状態に保つことによって実現されます。 上記の制限 (i) に準拠する3つのTX信号レベル (高、中、低) の組み合わせにより、6つの異なる信号レベルの組み合わせ (ワイヤ状態) が得られます。 ワイヤ状態の数6は、3つのTX信号レベルの置換です。 さらに、C-PHYエンコーダは、エンコーダルールに基づいて、フリップ、回転、極性シンボルを状態変化にエンコードします。

上記項目 (i)でシンボルごとに少なくとも1つのエッジが存在することを保証するには、C-PHY は1つのシンボルから次のシンボルに移動するときに必ず異なるワイヤ状態に遷移する必要があり、連続する2つのシンボルの間で同じワイヤ状態に留まることができません。この制限により、6つのワイヤ状態の間には5つの異なる遷移が存在することとなります。これは、エンコードされたデータには5つの異なる可能な状態があることを意味します。つまり、各シンボルには5つの取り得る状態があり、C-PHYはBase-5システム、つまり5進システムになります。その後、二進法と五進法の間を行き来します。これが、C-PHYマッパーが必要な理由です。 現在、Base-5システムを使用しているため、理論上の最大ビット/シンボル数は log2(5) = 2.3219です。マッパー関数は、マッピング率を理論上の上限に可能な限り近づけることができるように構築されました。さらに、マッパーは2つの整数間をマッピングする必要があります。上記の制限を達成するために、比率16/7 ≈ 2.28が選択されました。

これを別の方法で説明すると、マッパーは16バイナリビットを特定の数のC-PHYシンボルにマッピングする必要がありますが、シンボル(S)の数をどのように決定すればよいでしょうか? パラレルインターフェイスには 2^16の組み合わせがあり、マッパーの出力での組み合わせは 5^S => 2^16 であるため、S = 7になります。

C-PHYレシーバーがマルチ振幅シグナリングの振幅ではなく、入力信号の極性のみを検出する必要がある理由を理解するには、信号振幅にはデータが埋め込まれていないことを覚えておくだけで済みます。マルチ振幅シグナリングは、可能な遷移の数を増やし、シンボルごとに少なくとも1つの遷移が存在することを保証するためにのみ利用されます。

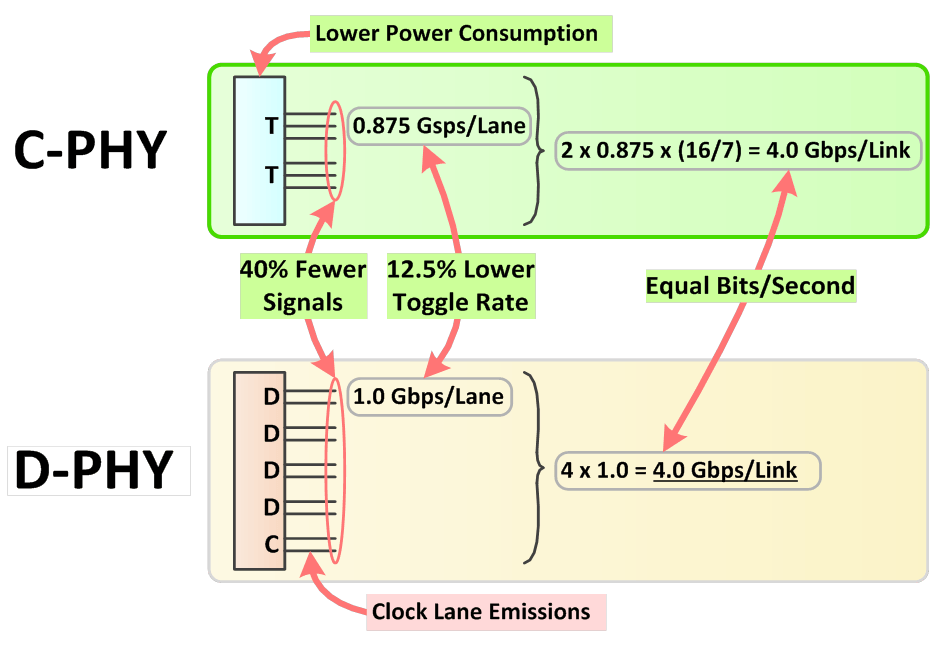

C-PHYとD-PHYのパフォーマンスを直接比較する1つの方法は、4.0Gbpsの総データレートをサポートし、同様の遷移レートで動作している場合を比較することです。 D-PHYの場合、これは4レーンD-PHYを使用し、10本のワイヤを使用し、各レーンが1.0Gbps/レーンで実行されることで実現できます。C-PHYで同じまたはそれより低い遷移レートで同じ集約データレートを取得するには、6ワイヤを備え、D-PHY の1.0Gspsよりも低い 0.875Gsps で動作する2レーンC-PHY を使用できます。この場合、C-PHYの合計データレートは 2 * 0.875 * 16/7 = 4Gbps になります。 この比較を以下の図6に示します。

この比較に基づくと、C-PHYはワイヤが少なく (最大40%少なく)、レーンあたりの遷移レートが低く (12.5%低く)、消費電力が低く (約20~50%低く)、レーン数が少ないことがわかります。 同じGbpsでも面積が小さくなり、クロックレーンからのエミッションがありません。

したがって、同じ総データレートで C-PHYとD-PHYを比較すると、C-PHYには多くの利点があります。ピンとボールの数が少なく (ピンあたりのパフォーマンスが向上するため)、各C-PHYレーンが独立しているため柔軟性があり、クロックが組み込まれているため、MIPI D-PHYと同じピン上で共存しながら、1つのリンクから1つのレーンを借用することが可能になります。C-PHY により、より高いデータレートのアプリケーションでも低電力化が可能になります。 さらに、C-PHYの組み込みクロックレーンにより、アプリケーションプロセッサ上の任意のレーンを任意のリンクに割り当てることができ、マルチバンドワイヤレスデバイスで特に重要となるクロックスプリアス放射が排除されます。

また、C-PHY の組み込み制御コードにより、高速バスターンアラウンド (BTA) 動作、時間に敏感なリンクの低レイテンシ (LRTE)、およびシングルエンドのLPモードを排除してより長い伝送距離を実現する代替低電力モード (ALP) などの新しい機能の効率的なサポートが可能になり、面積低減へと繋がります。最後に、C-PHY の低い遷移レートにより、多くの場合、製造が簡素化され、ローエンドカメラなどの低価格製品のコストが削減されます。

C-PHYとD-PHYの双方の個々の属性について説明しましたので、C-PHYとD-PHYの組み合わせの利点をいくつか挙げることにします。 これらには、シリアルインターフェイスピンの共有、LP (低電力) モードの再利用、共通ブロックの共有が含まれ、結果としてMIPI D-PHYとの互換性を維持しながら、面積の削減、電力/Gbpsの削減、MIPI D-PHYとMIPI C-PHY間のスムーズな移行、MIPI C-PHYの電力/パフォーマンス/エリア (PPA) の向上といった利点を享受することが可能になります。

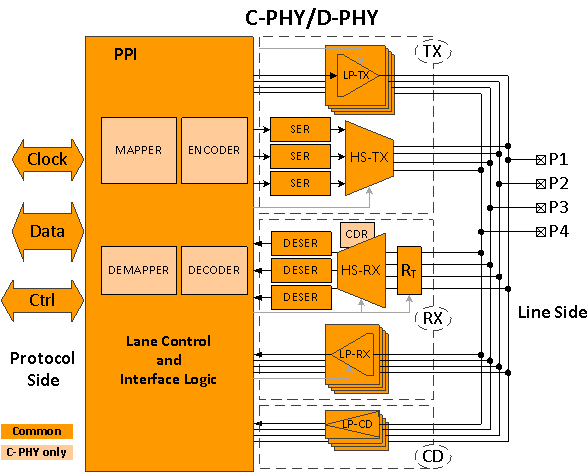

Mixel のC-PHY/D-PHYコンボ IPの実装は独創的です。すべてのD-PHYブロックはC-PHY動作 (HS-TX、HS-RX、SER、DESER、LP-TX、LP-RX、および LP-CD) に再利用され、C-PHYサポートのためのエリアオーバーヘッドを最小限に抑えます。すべてのブロックは再利用されましたが、エンコーダ、デコーダ、CDR、マッパー、およびデマッパーはC-PHY機能に必要な追加ブロックです。 Mixel実装のブロック図を以下の図7に示します。

コンボC-PHY/D-PHYは、Mixelによってさまざまなノードやファウンドリに実装されています。 実際にMixelのMIPI IPは、12の異なるノードと8つの異なるファウンドリでシリコン実証済みです。

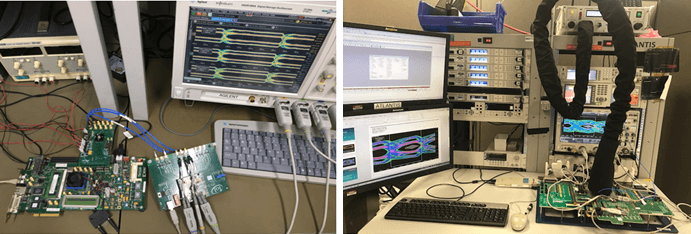

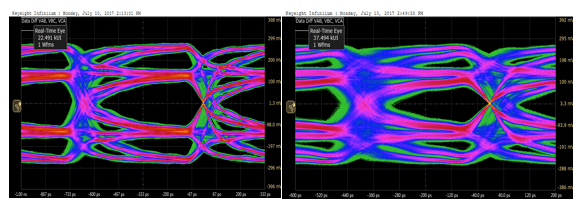

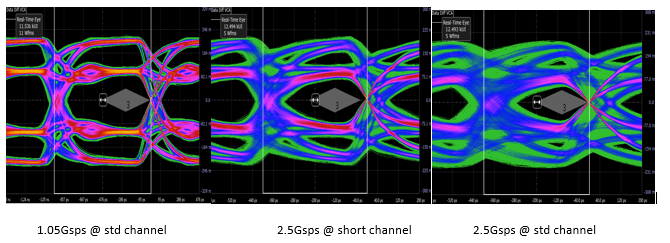

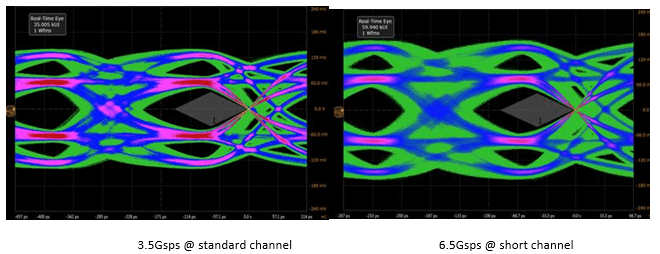

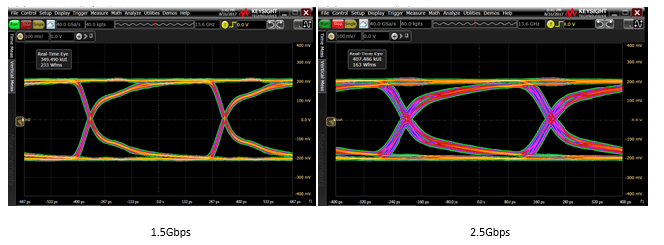

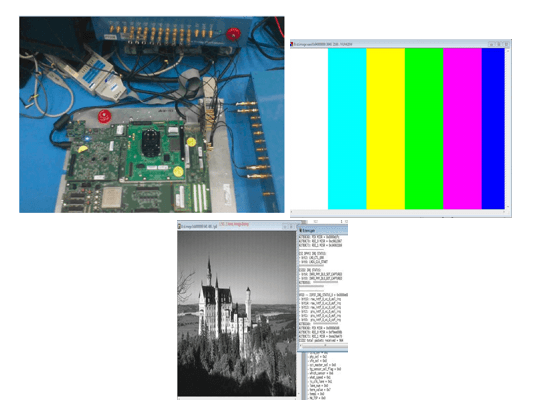

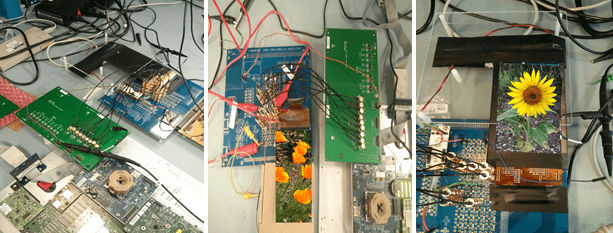

以下に、C-PHYおよびD-PHYトランスミッターのテストセットアップとシリコン評価環境を示します。

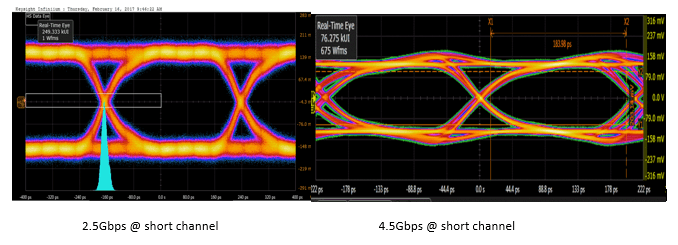

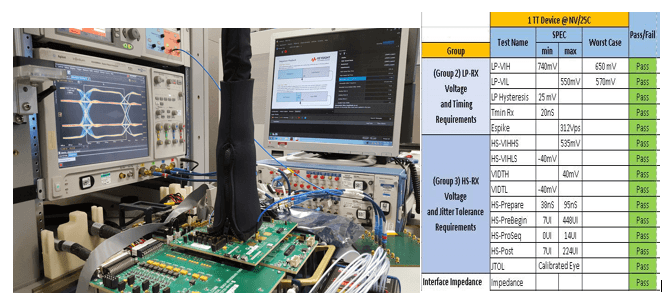

以下に、C-PHYおよびD-PHYレシーバのテストセットアップとシリコン評価を示します。

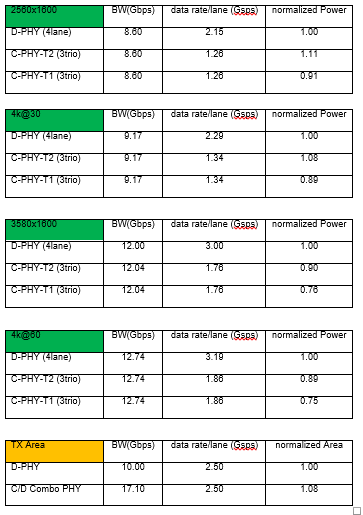

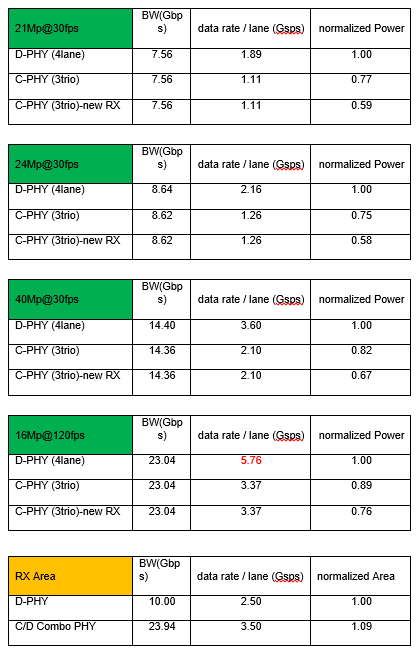

ここで、現在のディスプレイおよびカメラアプリケーションのさまざまなユースケースにおける電力、パフォーマンス、面積を見てみましょう。 これらをTable 3に示します。

同じデータレートでD-PHYとC-PHY/D-PHYコンボを比較すると、面積の増加はわずかです。 C-PHYのみのモジュールと同じGbpsで正規化して比較した電力は、ほぼ同等です。 C-PHYには、同じ遷移レートでD-PHYよりも高いデータレートを実現できるという明らかな利点があります。

ただし、コンボPHYの電力増加は、C-PHYモードコンフィギュレーションで複数のデザインオプションを有効にすることでキャンセルできます (ここには示されていません)。

Display

Camera

Notes:

- コンボPHY面積増加< 10%

- コンボPHYは広いレンジの解像度をカバー: 80Mpbs – 10Gbps – 17.1Gbps – 18Gbps – 23.94Gbps

- MIPI C-PHY モード: 低周波数、小バイアス、少レーン数により、D-PHYモードから~10-30% の電力低減。

- Courtesy of QUALCOMM

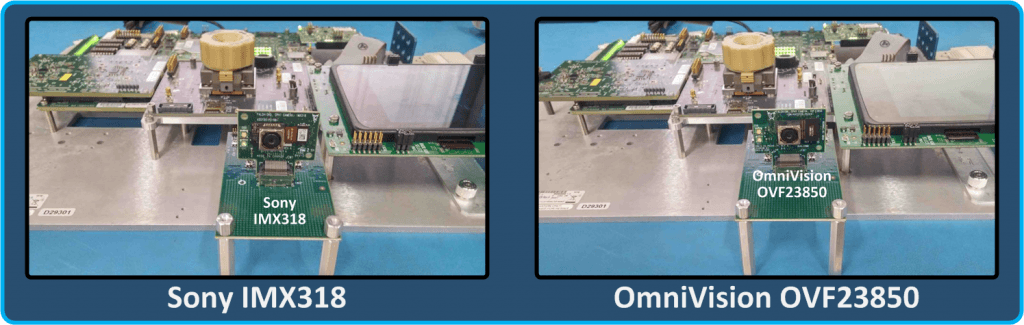

C-PHY/D-PHYコンボは、カメラ (Sony、OVT など)、ディスプレイ (ほとんどの大手DDIC企業と相互運用性テストが完了) を含む、さまざまなベンダーのさまざまなタイプの製品の複数のユースケースで広く採用が進んでいます。このエコシステムは、IP (Mixel)、AP/SOC (Snapdragon など)、テスター (Keysight、Tektronix、Introspect、The Moving Pixel Company)、およびコモンモードフィルター (Murata、Panasonic、TDK) を含む幅広い市場参加者によってサポートされています。

しかし、C-PHYの高いパフォーマンスは無料では得られません。C-PHYには、さまざまなデータレート範囲に合わせたプログラミングを必要とする独自の CDR、エンコードジッターを引き起こすマルチレベル信号伝送、PCB設計を複雑にする独自のトリオベースのシグナリングなどの課題があります。

結論として、MIPI C-PHYはより複雑で、より強力かつ効率的なPHYであり、C-PHY/D-PHYコンボはあらゆる点でさらに優れています。 Mixel は、デュアルモードMIPI D-PHY/MIPI C-PHYを開発し、シリコンで実証を済ませ、2つのPHY間のスムーズな移行を可能にします。 MixelのデュアルモードMIPI D-PHY/MIPI C-PHY はすべての共通ブロックを共有するため、面積が削減され、Gbpsあたりの電力が削減されます。 これは、MIPI D-PHYとの互換性を維持し、同じシリアルインターフェイスピンを使用しながら、MIPI C-PHY PPA の改善による利点を備えています。 さらに、MIPI C-PHY/MIPI D-PHYコンボは、複数のノードおよびファウンドリでシリコンで実証されており、多くのティア1 SOC、センサー、ディスプレイベンダーによってさまざまな最終製品に統合されています。デビュー以来、VR/AR/MR、自動車、IoTなどのモバイルおよびモバイル近傍アプリケーションを含むさまざまなアプリケーションにおいて、カメラとディスプレイの両方でMIPI C-PHY/MIPI D-PHYコンボの注目度の高まりを目の当たりにしています。

この記事を読んだ人はこちらの記事も読んでいます。

次世代VRディスプレイの課題 ―解決のカギはMIPIソリューション

携帯電話内部の高速データ転送,次の主役は「MIPI M-PHY」―― 広範なアプリケーションを見据えた多芸多才の標準規格

To learn more about Mixel’s silicon-proven IP, please visit mixel.com/ip-cores or Mixel’s contact page.