For more information, contact us here.

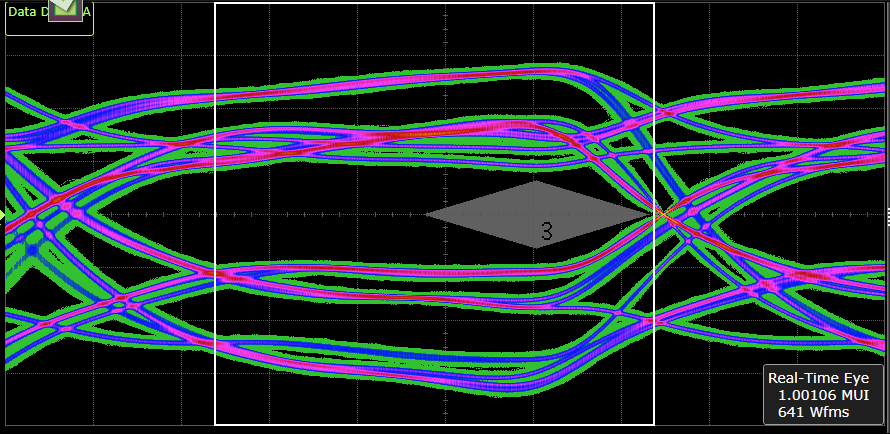

Running at 2.5Gsps

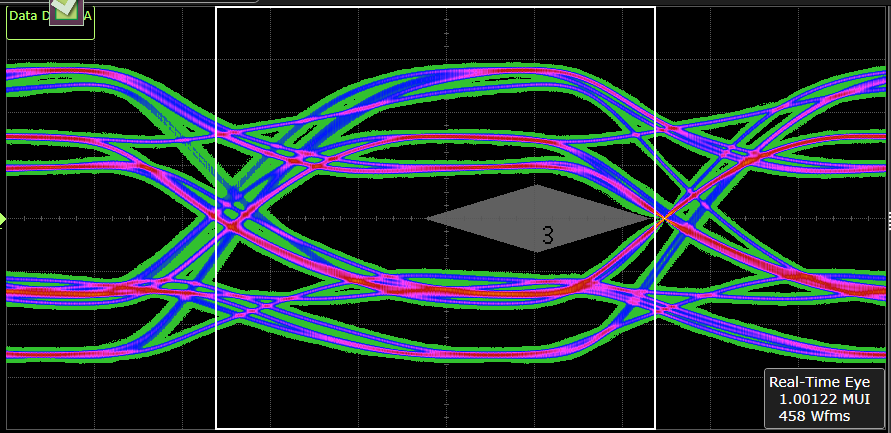

Running at 3.5Gsps

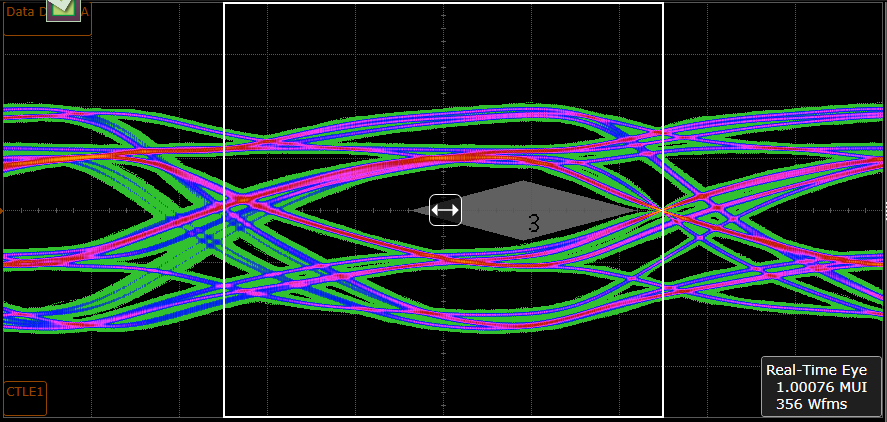

Running at 4.5Gsps

Running at 8.0Gsps

The Mixel MIPI C-PHY IP (MXL-CPHY) is a high-frequency, low-power, low cost, physical layer. (Learn more about Mixel’s MIPI ecosystem at Mixel MIPI Central which gives you access to Mixel’s best of class MIPI ecosystem supply chain partners.)

The C-PHY configuration consists of up to three lane modules and is based on 3-Phase symbol encoding technology, delivering 2.28 bits per symbol over three-wire trios and targeting a maximum rate of 8.0 Gsps, 18.24Gbps.

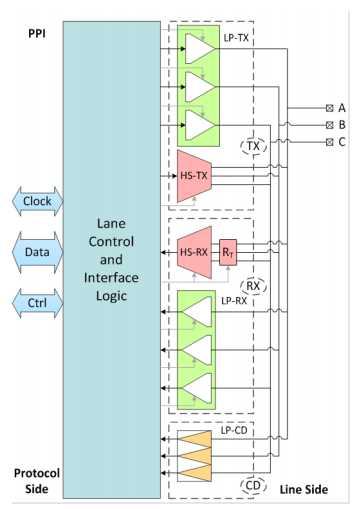

The C-PHY is partitioned into a digital module – CIL (Control and Interface Logic) and a mixed-signal module. The PHY IP is provided as a combination of soft IP views (RTL, and STA Constraints) for the digital module, and hard IP views (GDSII/CDL/LEF/LIB) for the mixed-signal module. This unique offering of both soft and hard IP permits architectural design flexibility and seamless implementation in customer-specific design flow.

The CIL module interfaces with the protocol layer and determines the global operation of the module. The interface between the PHY and the protocol is using the PHY-Protocol Interface (PPI). The mixed-signal module includes high-speed signaling mode for fast-data traffic and low-power signaling mode for control purposes.

During normal operation, a lane switches between low-power and high-speed mode. Bidirectional lanes can also switch communication direction. The change of operating mode or direction requires enabling and disabling of certain electrical functions. These enable and disable events do not cause glitches on the lines that would result in a detection of incorrect signal levels. All mode and direction changes are smooth to always ensure a proper detection of the line signals.

Mixel’s C-PHY is a complete PHY, silicon-proven at multiple foundries and multiple nodes. It is built to support the MIPI Camera Serial Interface (CSI) and Display Serial Interface (DSI).

The Mixel MIPI C-PHY (MXL-CPHY) Features:

- Support for MIPI® compliant C-PHY Specification Version 2.1 with backwards compatibility for MIPI C-PHY v2.0, v1.2, and v1.1

- Supports up to 3 lanes/trios

- Supports both high-speed and low-power modes

- 80 Msps to 8.0 Gsps symbol rate per lane in C-PHY high-speed mode

- Equivalent to 182.8 Mbps to 18.24 Gbps per lane in C-PHY high-speed mode

- 10 Mbps data rate in low-power mode

- Supports CSI-2, DSI, and DSI-2

- Low power dissipation

- Loopback testability (BIST) support

The Mixel MIPI C-PHY (MXL-CPHY) has many benefits including:

- Comprehensive embedded DFT features for allowing cost-effective high-volume manufacturing tests

- Support for full-speed internal loopback testability with minimal area overhead for high-volume manufacturing tests in the C-PHY Universal, TX+, and RX+ configurations

In addition, the Mixel MIPI C-PHY v2.1 has additional benefits including:

- Support for MIPI C-PHY v2.1 and MIPI C-PHY v2.0 features not available in previous versions of the specifications such as Spread Spectrum Clocking (SSC) and transmit equalization (de-emphasis)

- Support for new power saving functionality such as HS-TX half swing mode and HS-RX unterminated mode

- Support for new Alternate LP Mode, suitable for IoT applications with long channels, enabling Fast Bus Turnaround

Mixel’s MIPI C-PHY IP is also available as a MIPI C/D-PHY combo IP.

To learn more about Mixel’s silicon-proven IP, please visit Mixel’s contact page or read Mixel MIPI PHY related whitepapers here.

Mixel’s Production Ready Offering (“PRO IP”): MIPI C-PHY IP and MIPI C-PHY/D-PHY Combo IP

| C-PHY DSI TX (3T, 2.5Gsps) in TSMC 22ULL | More information |

| C-PHY DSI RX (3T, 2.5Gsps) in TSMC 22ULL | More information |

| C-PHY CSI-2 TX+ (1T, 2.5Gsps) in TSMC 40ULP | More information |

| C-PHY/D-PHY Combo DSI TX+ (3T/4L, 4.5Gsps/4.5Gbps) in TSMC N5 | More information |

| C-PHY/D-PHY Combo CSI RX+ (3T/4L, 4.5Gsps/4.5Gbps) in TSMC N5 | More information |

| C-PHY/D-PHY Combo CSI-2 RX+ (3T/4L, 6.0Gsps/4.5Gbps) in TSMC N6 | More information |

| C-PHY/D-PHY combo CSI-2 RX (3T/4L, 4.5Gsps/4.5Gbps) in TSMC N7 | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (3T/4L, 4.5Gsps/4.5Gbps) in TSMC 16FFC | More information |

| C-PHY/D-PHY Combo DSI RX+ (3T/4L, 4.5Gsps/6.5Gbps) in TSMC 16FFC | More information |

| C-PHY/D-PHY Combo Universal (3T/4L, 8.0Gsps/6.5Gbps) in TSMC 16FFC | More information |

| C-PHY/D-PHY Combo DSI RX (3T/4L, 2.5Gsps/2.5Gbps) in TSMC 22ULP | More information |

| C-PHY/D-PHY Combo CSI-2 TX (3T/4L, 2.5Gsps/2.5Gbps) in TSMC 22ULL | More information |

| C-PHY/D-PHY Combo CSI-2 TX (3T/4L, 4.5Gsps/4.5Gbps) in TSMC 28HPC+ | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (3T/4L, 3.5Gsps/2.5Gbps) in ST 28FDSOI | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (3T/4L, 3.5Gsps/2.5Gbps) in STM 40LP | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (2T/2L, 3.5Gsps/2.5Gbps) in STM 40LP | More information |

| C-PHY/D-PHY Combo CSI-2 TX (2T/2L, 1.5Gsps/1.5Gbps) in TSMC 40ULP | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (1T/1L, 2.5Gsps/2.5Gbps) in TSMC 40ULP | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (2T/2L, 2.5Gsps/2.5Gbps) in TSMC 40ULP | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (1L/1T, 1.5Gsps/1.5Gbps) in TSMC 65LP | More information |