MIPI D-PHYとMIPI C-PHYの最新技術動向を探る

著者:

Michael Nagib

AMS Director, Mixel, Inc.

Nuno Martins

Managing Director, Xpressphy

概要

高性能カメラとディスプレイ技術の急速な進化する分野において、MIPI D-PHY™およびMIPI C-PHY™仕様は引き続き先導的な役割を果たし、低電力、低遅延、高帯域幅のデータ伝送における基準を確立し続けています。前回の記事「MIPI C-PHY / D-PHY サブシステムを解き明かす」で得た知見を基に、今回はこれらの仕様の最新動向と、ビジョンおよびイメージング技術を変革する可能性について深く探っていきます。

市場動向が新たな機能の展開を後押し

MIPI D-PHYが15年以上前に導入された際、その主な目的はモバイル市場向けにシンプルで低電力、中程度の帯域幅を持つインターフェイスを創出することでした。2014年にMIPI C-PHYが導入されたことで、実装者はよりエネルギー効率の高いインターフェイスを使用して、損失の大きいチャネル上で動作させる選択肢を得ましたが、これには多少複雑さが伴いました。

その後、画像のダイナミックレンジ、ピクセル解像度、フレームレートの向上により、カメラとディスプレイに対するデータレート要件が急増しています。これらの向上は、ユーザーの見え方を向上させるだけでなく、リアルタイムの高度な画像処理を可能にするためにも不可欠です。したがって、MIPI D-PHYおよびMIPI C-PHYインターフェイスの主要な特徴の一つが、市場ニーズに対応するため、異なるバージョンにおいて最大データレートを継続的に向上させてきた点であることは驚くべきことではありません。

最近、これらのインターフェイスはモバイル市場を超えて拡大し、企業はシリコン設計、ソフトウェア開発、テストインフラへの投資を活用し、スケールメリットを享受できるようになりました。現在、MIPI D-PHYとMIPI C-PHYは、自動車(インフォテインメント、先進運転支援システム、自動運転)、産業(マシンビジョン、ロボティクス、監視)、没入型ヘッドセット(拡張現実/AR、仮想現実/VR、混合現実/MR)、医療、およびモバイルの影響を受ける他の市場において採用されています。このような広範な応用分野は、インターフェイスの進化を促進しており、省電力機能、長距離伝送能力、ピン数の削減などへの注目が高まっています。

これらの新規市場への展開は、モバイルアプリケーションでは通常遭遇しなかった課題を追加でIPおよびICベンダーに課しています。例えば、自動車用の安全性の重要なアプリケーションでは、故障率を低減するためにより大きなシグマ変動に対応した設計、故障検出のための安全機構の組み込み、より広い接合温度範囲での動作、および10~15年間の動作信頼性の確保が求められます。これらの新たな要件は、機能安全に焦点を当てたISO26262や、自動車用集積回路のストレステストを規定するAEC-Q100などの業界標準によって対応されています。さらに、ベンダーは電磁両立性(EMC)を考慮し、高速データリンクが他の電子システムと干渉しないようにする必要があります。

市場動向に常に注目し、インターフェイスを適切に最適化することで、MIPI D-PHYとMIPI C-PHYは、6G、人工知能(AI)、モノのインターネット(IoT)など、新たな技術革新の時代への移行においても、その重要性を維持しています。

MIPI D-PHYの最新の機能

MIPI® 短距離物理インターフェイス ファミリーにおける高機能モデルであるMIPI D-PHY は、2009年にリリースされ、即座に成功を収めました。このインターフェイスは、モバイルアプリケーションにおけるカメラとディスプレイの高性能かつ低コストな接続の基盤となるフレームワークを確立しました。このインターフェイスの根本原理は、規格の初期バージョンからほぼ変更されていません。ソース同期型ダブルデータレート(DDR)の特性を維持し、高スループットのデータ通信用にSLVS差動信号方式を採用したハイスピード(HS)モードと、制御目的用にSpaced-One-Hot LVCMOS信号方式を採用したローパワー(LP)モードを備えています。

データレートの向上

より高い帯域幅への需要により、新しい仕様バージョンは主にデータレーンあたりの最大ビットレート向上に重点が置かれました。MIPI D-PHY v1.2の2500 Mbpsからv2.xの4500 Mbpsへ、そして最終的にv3.xの標準リファレンスチャネルで9 Gbpsへと向上しました。チャネル長が短くなれば、さらに高いレートが実現可能で、v3.0以降では最大11 Gbpsが規定されています。当然ながら、製品形態や克服すべき物理的な距離は基本的に同じであったため、物理チャネル特性は変更されませんでした。データレートの向上をサポートし、内在する高い信号損失と歪みを軽減するため、信号イコライゼーション機能が導入されました。

イコライゼーション・オプション

MIPI D-PHY v2.0では、トランスミッター側でのイコライゼーションが信号のデエンファシス形式で初めて定義され、2.5 Gbpsを超えるデータレートにおいて、高周波(HF)と低周波(LF)の信号比を3.5dBまたは7dB増幅させる機能を備えています。v3.0では、レートが9~11 Gbpsまで向上したため、受信側にも連続時間線形イコライゼーション(CTLE)が追加され、全体的なチャネルイコライゼーションをさらに向上させました。TXのデエンファシスとRXのCTLEの組み合わせは、インターコネクトだけでなくパッケージやシリコントランシーバーの寄生負荷を含む、チャネルの全体的な周波数応答を平坦化するために一般的に使用されます。

最新のMIPI D-PHY v3.5では、レシーバーリファレンスイコライザにおいて非線形判定帰還形イコライゼーション(DFE)の使用が導入されました。これにより、実装者は実際のレシーバー設計においてこのような技術を採用することでメリットを得られる可能性があり、特に6 Gbpsを超える設計において有効です。さらに、この規格は、以前のバージョンの仕様に準拠した設計においてこれらの技術の使用を禁止しておらず、後方互換性と実装の柔軟性を確保しています。

低電力機能

新しい低電力機能が導入され、エネルギー/ビット効率の向上を実現しつつ、シリコンプロセス技術の進歩に合わせたインターフェイスの最適化と、現代の課題に対応しています。これらの機能には以下のものが含まれます:

- Half-swing mode: 高速トランスミッターの信号振幅が半分に低減されます。これは、低速かつ短距離の接続において特に有用です。

- RX unterminated mode: レシーバー側で100オームのインピーダンスが無効化されています(TX Half-swing modeが必要)。

- Low Voltage Low Power (LVLP) mode: 低電力LVCMOSトランスミッターの出力電圧は、先進的なCMOSプロセスにおけるコア電源に適応するため、標準の2Vから低減されています。

MIPI D-PHYが当初1.2V LVCMOS信号を採用した際、当時のほとんどのシリコン技術でこのような電圧レベルが広くサポートされていました。しかし、より先端のプロセスジオメトリが登場するにつれ、いくつかの問題が浮上してきました。まず、これらのプロセスにおけるコア電源電圧は1.2Vを大幅に下回る場合があり(例:5nmプロセスでは0.75V)、I/O電源ドメインからの電圧調整が必要となり、その欠点が伴います。次に、1.2V信号伝送はこれらのプロセスにおけるコアデバイスに過大な負荷をかけ、IOリーク電流の増加やデバイス寿命の短縮を招く可能性があります。第三に、このような高レベルのレール・トゥ・レール信号伝送は、サポート可能なチャネル長を大幅に制限します。最後に、1.2V信号伝送はトランスミッター側とレシーバー側の両方に専用の回路を必要とし、パッド出力への負荷増加により、最大到達速度がさらに低下します。

LVLPは、LVCMOS信号レベルを0.95Vまで下げることで、これらの問題の一部を解決する過渡的な機能でした。しかし、HSとLP信号レベルの正しい区別を損なうことなく、さらにスケーリングすることはできませんでした。これらの課題に対処するため、MIPI D-PHY v2.5は「Alternate Low-Power(ALP)モード」と呼ばれる新しい動作方式を導入しました。このモードでは、LP信号とその関連回路は使用されなくなります。代わりに、高速通信用に用いられるHS-TXおよびHS-RX回路がその機能を担います。高速モードと同様の信号レベルを使用することで、高度なジオメトリにおける適合性、信頼性、および過剰なリークが軽減され、IoTチャネルで最大4メートルの通信距離を実現可能です。

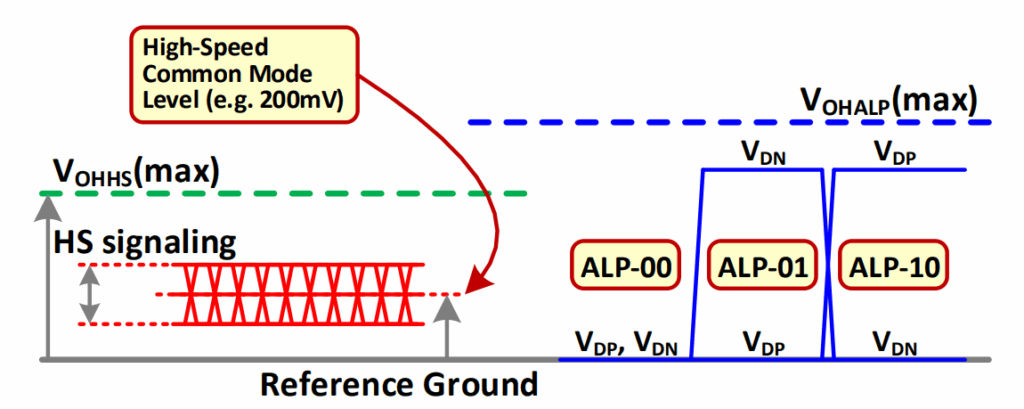

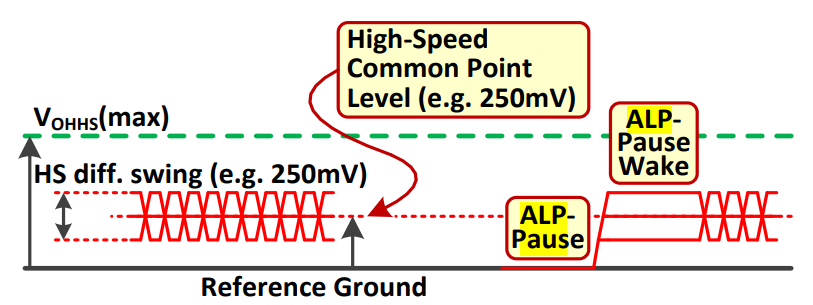

ALPモードでHS-TX機能を再利用しているにもかかわらず、ALP信号伝送中にHS-RXが終端されていないという特徴があります。これは電力消費を削減するためであり、ラインレベルが常に差動ではない点に注意が必要です。以下の図に示すように、ALP-00状態では両方のラインが同時に接地される状態が存在します。

ALP-00は、従来のLP停止状態およびULPS状態の直接的な置き換えとして機能します。トランスミッターによってアクティブに駆動され、両方のラインを接地することで、コモンモード電圧がゼロで差動振幅もゼロの差動状態を生成します。この状態は、長時間の非アクティブ状態の電力削減に不可欠です。

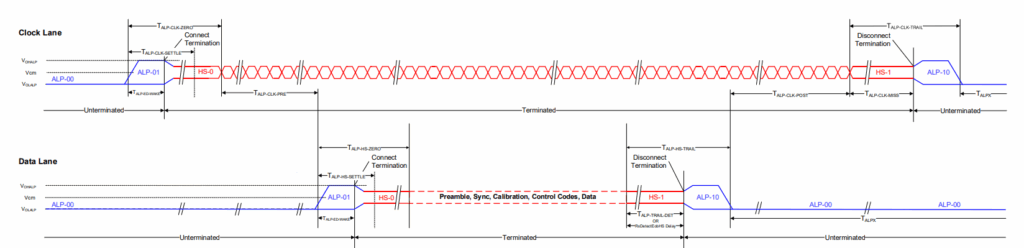

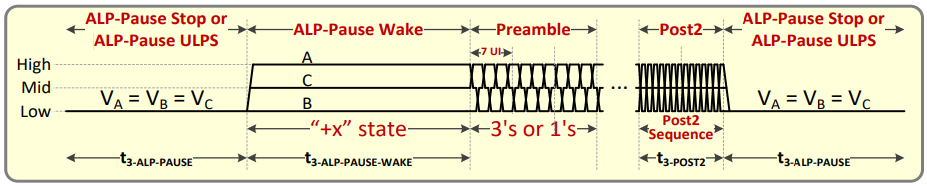

図2に一般的なバーストフォーマットが示されており、クロックレーンと代表的なデータレーンが示されています。両レーンはALPStop状態(ALP-00)から開始され、長時間の非アクティブ状態を維持できます。データまたは制御情報の送信準備が整うと、まずクロックレーンがALP-01Wakeパルスを送信して起動し、その後、転送された高速クロックが安定すると、データレーン(複数可)でも同様のWakeパルスが送信されます。レシーバー側のリンクパートナーは、特殊な出口検出器(ALP-ED)を使用してALP-01Wakeパルスを検出し、その後、高速通信(データ、制御コード、キャリブレーションパターンなど)の準備として差動終端が有効化されます。

通信は、長いHS-Trailシーケンス(HS-1/ALP10)の送信と、ALPStop状態への遷移で終了します。この際、データレーンが最初に遷移し、その後クロックレーンが遷移します。各レーンのレシーバーはバーストの終了を検出し、HS-Trailシーケンス中に終端を無効化します。このプロセスは、追加のデータや制御バーストを送信するために必要に応じて繰り返し実行されます。

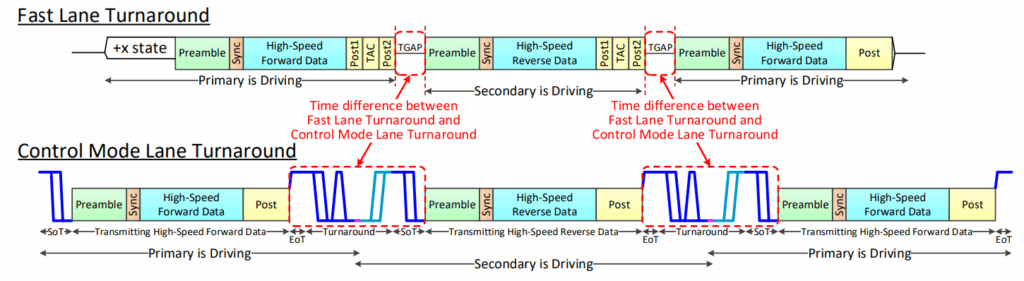

ALPのもう1つの、あまり目立たないが同様に重要な利点は、双方向レーンモジュールを使用するアプリケーションにおけるレーンターンアラウンド時間の短縮です。LPモードでは、レーンターンアラウンドは50nsの持続時間を持つ固定パターンの低電力状態に依存しており、これは高速データレートに対応できません。ALPは、埋め込まれた16UI制御コードを含む制御バーストを使用した「高速レーンターンアラウンド」の概念を導入します。1Gbpsでは、従来のLPモードと比較してターンアラウンド時間が約半分に短縮され、さらに高い動作レートではさらに短縮されます。これにより、従来のLPモードでは1us以上かかっていたターンアラウンド時間が、ALPモードでは数百ナノ秒にまで短縮されます。

高速レーンターンアラウンドとALP機能の連携により、MIPI CSI-2®(カメラシリアルインターフェイス)の新たな利用モデルが実現され、ユニファイドシリアルリンク(USL)などの機能が利用可能になります。この革新により、データ通信とサイドバンドのカメラ制御インターフェイス(CCI)を同じ高速リンク上で伝送することが可能となり、配線数を削減し、チャネルの到達距離を延長できます。

MIPI D-PHYなどの転送クロック・インターフェイスは、連続的なトグル動作を行うクロックの存在により、高いEMI放射が発生しやすい傾向にあります。システムレベルのシールドでこの問題をある程度軽減することは可能ですが、MIPI D-PHYはバージョン2.0からスペクトラム拡散機能を導入しました。このアプローチでは、クロックソースの周波数は通常、三角波プロファイルで変調され、信号エネルギーをより広い周波数範囲に分散させることで、任意の周波数におけるピーク放射レベルを低減します。ダウン・スプレッド・プロファイルは、ピーク偏差 -5000ppmおよび変調レート30~33KHzで規定されています。

Embedded Clock Mode

2023年5月、MIPI D-PHY v3.5が導入され、新たなEmbedded Clock Mode(ECM)が採用されました。これはD-PHYアーキテクチャにおける重大な変更点です。後方互換性を維持するためForwarded Clock Mode(FCM)は維持されましたが、ECMではデータストリーム内にクロックタイミング情報を埋め込み、レシーバー側でClock and Data Recovery(CDR)ユニットにより復元されます。この変更により、以下のメリットがもたらされました:

- Reduction of EMI emissions: 転送されたクロックレーンの抑制により、電磁干渉を低減

- Relaxed skew alignment: レーン間のタイミングが独立

- Reduced wire count: 2ピンの最小構成が実現可能

- Increased data throughput: クロックレーンをデータレーンとして再利用することで、レーンごとのデータレートを増加させずに、一般的な10ピン構成(4データ+1クロック)において、総データスループットを25%向上

MIPI D-PHYの元の動作フレームワークにおける根本的な変更を踏まえ、新しいECMモードとFCMとの共存方法について詳しく解説します。両モードはMIPI D-PHY v3.5においてオプションとして定義されており、同じインターコネクトと電気的仕様を共有しています。これにより、特定のPHYはFCM、ECM、またはその両方をサポートする可能性があります。実質的に、v3.5はMIPI D-PHYで初めて、プライマリデバイスとセカンダリデバイス間の後方互換性を完全に保証しないバージョンです。新しいv3.5 PHYでECMのみを実装するものは、古いv1.x~v3.0 PHYと互換性がありません。ECMとFCMの両方をサポートするPHYの場合、2つのモード間の動的な遷移は発生しません。初期化時に1つのモードが選択され、その選択は維持されます。

Forwarded Clock ModeからEmbedded Clock Modeへの移行に伴い、一部のレガシー機能の廃止またはサポートされなくなります。これには以下の機能が含まれます:

- 高速双方向通信

- Alternate Low Power(ALP)モード

- スキューキャリブレーションとFCMレガシー・プレアムブル・シーケンス

MIPI D-PHY ECMは、データストリームにクロックタイミング情報を埋め込むため、他の業界標準と同様に128b132bラインエンコーディングと暗号化を採用しています。各132ビットのブロックは、ライン上でシリアルに送信され(左端の最下位ビットから先頭)、各ブロックは4ビットのヘッダーと128ビットのペイロードで構成されています。ヘッダーは制御用に4’b0011、データ用に4’b1100を使用し、冗長性による1ビットのエラー訂正を提供します。これにより、コーディングによる3.125%のオーバーヘッドが生じます。

プロトコルデータは、多項式 G(x)=x23 + x21 + x16 + x8 + x6 + x2 + 1 およびシード 0x1DBFBC を使用して暗号化されます。このシードは、パケット開始制御コード (STP) の送信時にリセットされます。プロトコルから欠落しているデータは、128 ビットのペイロードを完了するために、ゼロ値のビットでパディングされます。

制御データは暗号化されていません。32ビットの制御ワードを4回複製し(2回は反転、2回は非反転)、DCバランスとエラー耐性を確保しながら128ビットのペイロードを構成します。

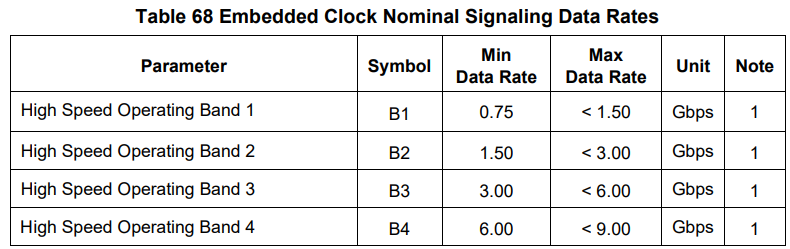

PHY-プロトコルバッファリングのコストを大幅に増加させるギアベースのインターフェイスを回避するため、D-PHY ECMは4つの動作バンドを備えたバンドベースのインターフェイスを定義しています。センサー/ディスプレイPHYは単一のバンドを実装を選択できますが、アプリケーションプロセッサ(AP)PHYはサポートされる最高バンドまで全てのバンドを実装する必要があります。トランスミッターは選択したバンド内で1つのデータレートをサポートするだけで済みますが、レシーバーはサポートされるバンド内のすべてのレートで動作する必要があります。これらの関係は、システムの全体的なコストを抑えつつ相互運用性を確保します。

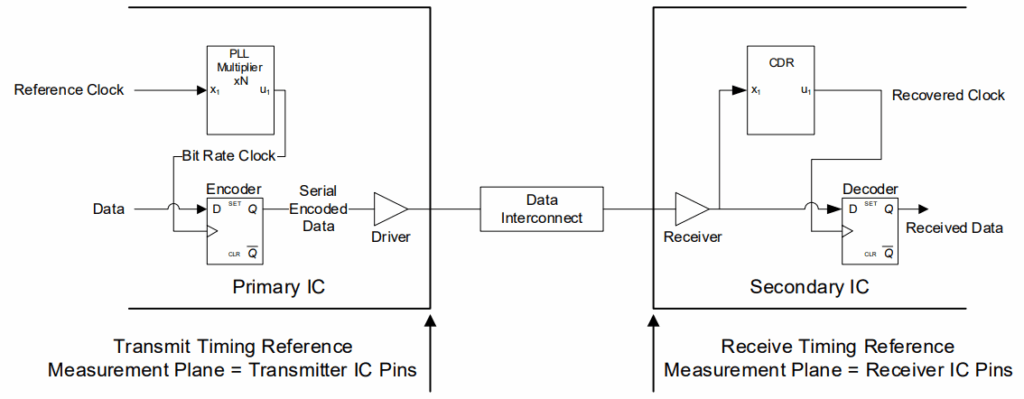

インターフェイスのバンドベースの性質のため、各セカンダリPHYインスタンスでリファレンスレスCDRを使用可能です。このユニットは、4つの定義されたバンドのいずれかのレートで入力ビットストリームに同期します。これは、セカンダリIC PHYを特定のレートで動作するように事前プログラミングする必要がないため、PLL設計の要件を緩和する点で重要です。さらに重要なのは、局所的な水晶リファレンスの必要性を排除し、全体的な設計を簡素化し、コストを削減する点です。

図7に示される一般的なECMバーストシーケンスは、FCMの多くの側面とタイミングを継承しています。LP部分は変更されておらず、最も大きな変更はHS部分で発生しています。STP(パケット開始)とEDP(パケット終了)が符号化データを区切っており、RXでCDRを同期させるための初期INIT-TRAINシーケンスが使用されます。INIT-TRAINシーケンスは1010…で、EMIが懸念される場合はPRBS9がオプションとして選択可能です。その持続時間は、前回のバースト送信からの累積クロックドリフトが25000ppmを超えないように指定され、短時間または長時間シーケンスにプログラム可能です。FCMと同様にデータスロットリングは存在しないため、PHYは高速モードでプロトコルデータまたは制御コードを継続的に送信し、長時間の非アクティブ期間中はLP-11に移行します。トレーニングシーケンスが非常に長いため(数千UI)、過去FCMで実施されていたような頻繁なLP-HS-LP遷移は現在では現実的ではありません。したがって、インターフェイスは高速モードで継続的に動作するメリットがあり、プロトコルは送信する実際のデータがない場合にフィラー/アイドルコードを導入します。

データストリーム内にクロックタイミングを埋め込むことで、ECMは性能を向上させ、設計要件を簡素化し、D-PHYが堅牢で適応性の高いソリューションとして機能し続けることを保証します。

MIPI D-PHY 機能の進化のまとめ

以下の表は、仕様バージョンごとにD-PHYの主要な機能を要約したものです。

MIPI C-PHYの最新の機能

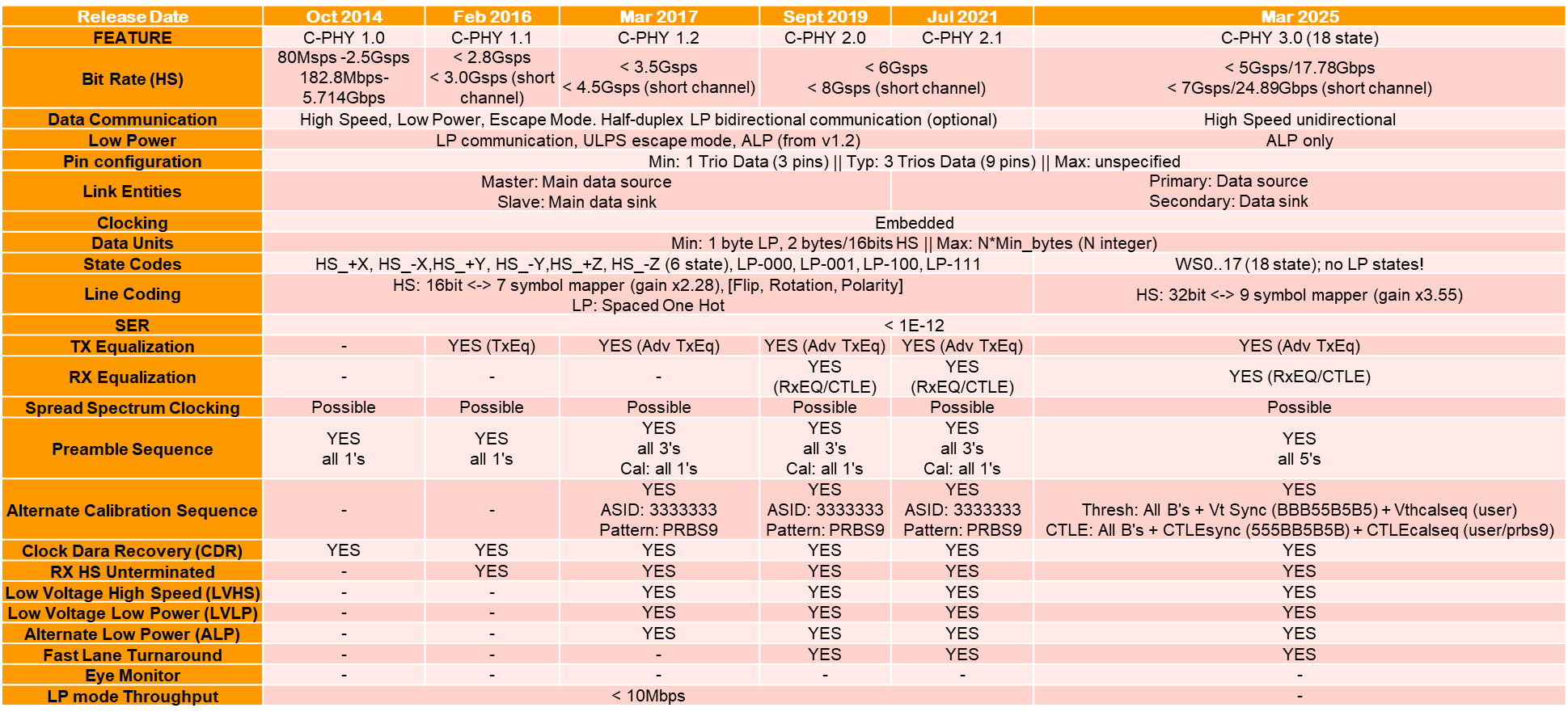

MIPI C-PHY v1.0がリリースされてから10年以上が経過し、MIPI D-PHYと同様に、その動作速度の向上に向けた取り組みが進められてきました。MIPI C-PHYでは多相/レベル符号化が採用されており、従来各シンボルに約2.28ビットが詰め込まれていました。そのため、シンボルレートはMIPI D-PHYほど向上していませんが、同様のピン数を持つインターフェイスにおいて、C-PHYの総帯域幅はD-PHYを常に上回っています。

シンボルレートとイコライゼーションオプション

元の2.5ギガシンボル/秒(Gsps)×2.28=5.7Gbps/レーンというレートから、MIPI C-PHYはバージョン1.1で2.8Gsps、バージョン1.2で3.5Gspsへと進化しました。これは、2つの異なるTXイコライゼーション方式とレシーバーを微調整するための特殊なトレーニングシーケンスを採用することで実現されました。バージョン2.xでは、レシーバー側でCTLEを追加することでチャネルのイコライゼーションをさらに改善し、標準リファレンスチャネルのシンボルレートが6Gsps(約13.7Gbps/レーン)に増加しました。

低電力機能

低電力分野において、MIPI C-PHYはMIPI D-PHYとの互換性を維持しました。v1.1では、低速時における終端なしでのRXを動作できる機能が導入されました。v1.2以降、新たな機能が追加されました:コモンモードと差動信号の振幅をMIPI D-PHYのレベルに合わせるため(特にコンボ実装において重要)にLow Voltage High Speed(LVHS)モード、LVCMOSレベルを低減するためのLow Voltage Low Power(LVLP)モード、そして最後にAlternate Low Power(ALP)モードです。

ALPはMIPI C-PHYにおいて、以前にMIPI D-PHYで説明したものと同様の問題に対処しますが、解決方法は若干異なります。これは、MIPI C-PHYのレーン信号イベント用に予約語を活用しているためです。ラインレベルは図9に示されています。MIPI D-PHYとの類似点もありますが、ALP-PauseとALP Wakeパルスの概念は共通しています。ただし、重要な違いがあります:ALP PauseではVA=VB=VCのみが必要であり、これはAB、BC、CAペアの差動振幅の崩壊を意味しますが、MIPI D-PHYのような接地レベルを必ずしも意味するわけではありません。Wake状態は通常+Xで、Aラインがハイレベル、BがローレベルのためVAB = Vod_strongレベルとなり、Cラインは中間レベルになります。

図10に、3本のワイヤ(A、B、C)からなる単一のデータレーン用の汎用ALPバーストフォーマットを示します。レーンは常にALP-Pause Stop(またはULPS)スタンバイ状態から開始され、従来のLPモードと類似していますが、前述のように異なるラインレベルを使用します。バーストは、リモートレシーバーを起動させるために十分な長さの期間、+X状態を送信することから始まります。このレシーバーは通常、ラインの状態を監視するために低電力検出器を使用しています。MIPI D-PHYとは異なり、MIPI C-PHY ALPモードではレシーバー側終端の動的切り替えは行われないため、バースト全体を通じて弱い電気レベルと強い電気レベルは一定に維持されます。

+X Wake状態の後、ALPデータ/コマンドバーストまたはキャリブレーションバーストが送信されるかどうかに応じて、all-1’sまたはall-3’sのプレアムブルが送信されます。バーストの種類に関わらず、最終シーケンスとして7UI StopまたはULPSコードに続き、プログラマブル長さのPOST2フィールドが送信され、レシーバーにリンクがスタンバイ状態の1つに戻ることを示します。このシーケンスは、データをプロトコルまで処理してフラッシュするために十分なトレーリング・クロック・エッジを提供します。

その間、高速データまたは特定の機能を表す予約シンボルシーケンスがリンクパートナーに送信されます。これらの予約シーケンスの一つがターンアラウンドコード(TAC)で、プライマリ側が送信を停止し受信状態に移行する一方、セカンダリ側が補完状態に移行するファスト・レーン・ターンアラウンド手続きを開始します。この手続きは、MIPI D-PHYで確認されている利点と類似しており、特に従来のLP制御モード・レーン・ターンアラウンドと比較して操作の遅延を削減します。これは、LP状態の長い持続時間に制約されないためです。

MIPI D-PHYプロトコルとは異なり、MIPI C-PHYは専用の制御バーストを必要とせず、そのコーディング構造を利用して、元の向きで送信される最後のデータバーストにTACコードを埋め込むことで、バス方向の反転に必要な時間をさらに短縮します。以下の図11は、ALPモードにおけるターンアラウンド手順とレガシーLPモードを比較したものです。

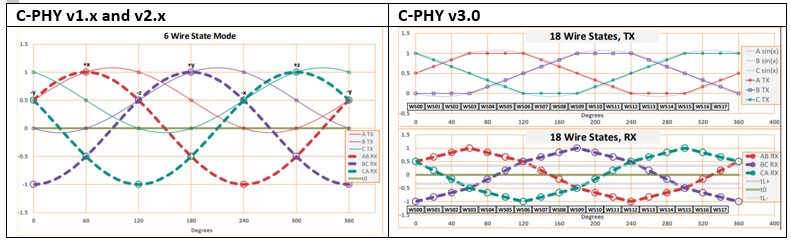

データレート向上(18-Wirestate)

帯域幅の需要が継続的に増加する中、MIPI C-PHY v3.0は2025年3月にリリースされました。このバージョンは、元の6ワイヤ状態から18ワイヤ状態への拡張を基盤とした、完全に新しいアーキテクチャを採用しています。この変更の目的は、MIPI C-PHYのビットレートを向上させつつ、シンボルレートを維持またはやや低下させ、以前のバージョンと同じチャネル上で動作させることです。このアーキテクチャの根本的な変更にもかかわらず、6フェーズモードで動作する場合、以前のバージョンとの後方互換性が維持されています。

では、この新しいアーキテクチャはどのようなものなのでしょうか?ビットレートの向上はどのように実現されているのでしょうか?シリコンコストを削減する最適化された方法で、旧アーキテクチャと共存できるのでしょうか?これらの疑問を、6-Wirestateと18-Wirestateのソリューションを比較することで探っていきましょう。

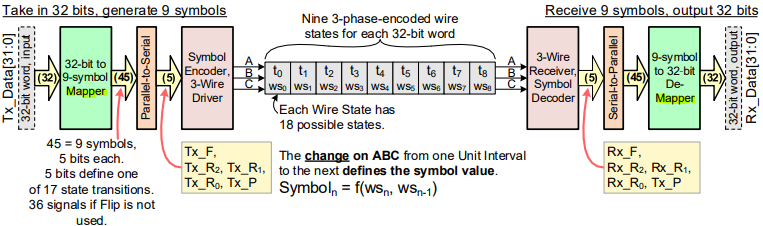

MIPI C-PHYの以前のバージョンでは、コントローラーからの16ビットのデータを7つのシンボルグループにマッピングし、16/7 = 2.28倍の符号化利得を実現していました。符号化には6つのワイヤ状態(+X、-X、+Y、-Y、+Z、-Z)が使用され、トリオ内の各ワイヤは3つの可能な電気レベル(High、Middle、Low)のいずれかを選択していました。

ビットレートを向上させつつシンボルレートを維持するため、新しい18-Wirestateモードでは、コントローラーから送信される32ビットのデータを9つのシンボルグループにマッピングし、32/9 = 3.55倍の符号化利得を実現しています。インターフェイスにおける物理リソースの増加はなく、各レーンあたり同じ3本のワイヤ(トリオ)が使用されます。ただし、これらのワイヤは7つの可能な信号レベルのうち1つを採用し、AB、BC、CAの差動ペア(WS0…WS17)に対して18のユニークなレベル組み合わせを生成します。

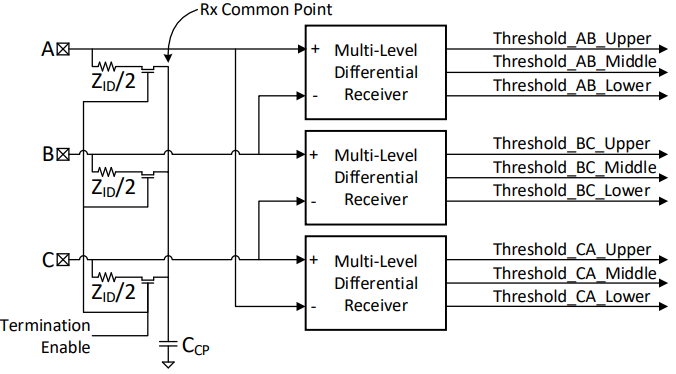

図12は、両方のソリューションにおけるコンステレーションの違いを示しています。6-Wirestateモードでは、シンボル検出のためにAB、BC、CAの信号ペアの極性(+/-)のみを決定する必要がありました。しかし、18-Wirestateモードでは、信号振幅にも情報が符号化されており、各状態を明確に識別するために、追加の2つの振幅閾値(tL+とtL-)との比較が必要です。各ラインのペアに配置されたレシーバーは、実質的にマルチレベルスライサーとして機能し、4つの可能な値のいずれかを出力します。

各シンボルにつき少なくとも1つのエッジ遷移を確保するため、MIPI C-PHYはワイヤ状態を継続的に切り替えます。これにより、合計17の遷移が符号化されます。32ビットをラインシンボルにマッピングするには、少なくとも2³² ≈ 4.295×10⁹のユニークな組み合わせが必要ですが、使用される9つのシンボルそれぞれに17の可能な遷移を提供する方式では、合計17⁹のユニークな組み合わせが生成され、この要件を大幅に上回ります。実際、MIPI C-PHY v3.0はトランジションのジッターを低減し、内部データパスの幅を最小化するため、一部のシンボルの使用を制限しています。これにより、12進数システムとなり、129 ≈ 5.15×10⁹の組み合わせでも、すべての可能な32ビット組み合わせを符号化するのに十分です。

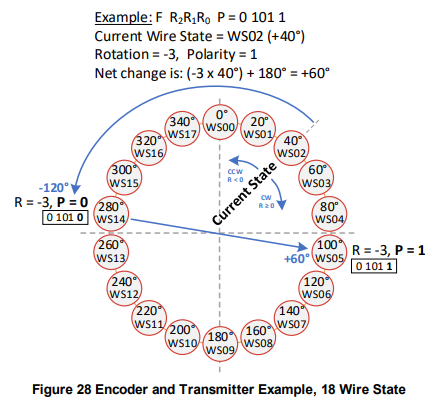

32ビットと9シンボルの変換はマッピング関数を通じて実現され、各シンボルは17通りの二進値(5’b00000-5’b10000)を持つ5ビットのコードで表されます。 各ビットは、Wire状態変更パラメーター(Flip、Rotation、Polarity:F、R2、R1、R0、P)に対応し、6-Wirestateモードと同様の仕組みです:

- Polarity (lsb): ワイヤの状態の極性を維持(1’b0)または、180°回転(1’b1)

- Rotation: 2の補数における[R2, R1, R0]の回転方向と回転量:

- -1から-4まで、-40°から-160°の回転

- 0から3まで、+40°から+160°の回転

- Flip (msb): 次の状態(1’b1)を180°回転させ、回転方向と極性を無視

シンボル情報は、連続する2つのワイヤ状態の遷移中に取得されます。図13はこの概念を説明しており、マッパーから出力される5’b01011で符号化されたシンボルが、現在の状態WS02から次の状態WS05への遷移を引き起こします。マッピング関数は、復元されたクロックにおける誘起されたジッターがより大きいため、シンボル『0』、『7』、『9』、および『E』を除外します(これらは位相図における±20°および±40°の回転に対応します)。180°回転またはFlipパラメーターに対応する『G』シンボルも除外されます。この除外により、シンボルデータパスを45ビットから36ビットに削減することで実装が簡素化されます。

図14は、18-Wirestateモードにおける新しい(デ)マッピングおよび(デ)コーディング機能を示しています。

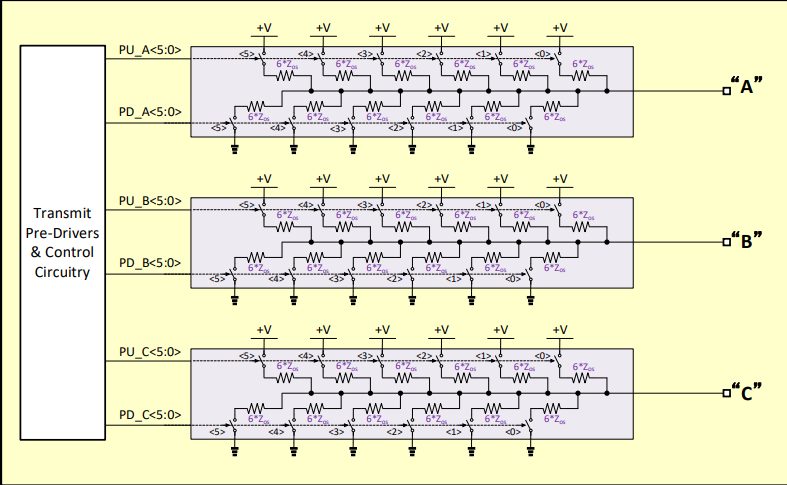

電気的な観点から、トリオ内の各導線は、7つの等間隔の電気レベル(LSL0からLSL6)のいずれかに駆動されます。いずれの時点においても、すべての導線は異なるレベルにあり、これによりすべての差動レシーバーに非ゼロ電圧が維持され、伝送中の導線状態(WS00からWS17)に関わらず、コモン電圧が一定に保たれます。

18-Wirestateライン・ドライバーは、6-Wirestateドライバーの自然な拡張版であり、プリ・ドライバー回路によって個別に制御される6つのプルアップ/プルダウン・レグを組み込んでいます。各レグの出力インピーダンスは、標準の差動インピーダンスの6倍高く、6-Wirestateモードで必要な「ハイ」「ロー」「ミッド」レベルを容易に生成できます。18-Wirestateモードでは、トランスミッター・デエンファシスが使用されることは想定されていません。

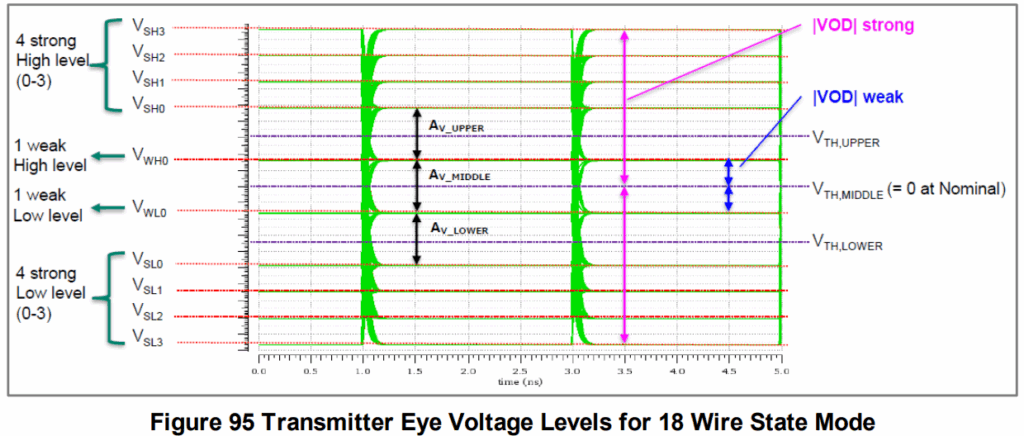

各レシーバーには現在、10の差動レベルが設定されています:強めのHighが4つ、弱めのHighが1つ、強めのLowが4つ、弱めのLowが1つです。さらに、図16に示すように、関連する3つのアイ・ダイアグラム(Upper、Middle、Lower)が存在します。当然ながら、レベルの数が増加すると送信電力の増加が必要となり、VODの最も強いレベルは6-Wirestateモードに比べてほぼ2倍になっています。

さまざまな信号レベルにもかかわらず、各レシーバーは3つの異なる閾値レベルを使用して、アイダイアグラムを垂直に分割し、4つの可能な出力のうち1つを生成するために、4つの異なる電圧範囲(Strong High、Weak High、Weak Low、Strong Low)を区別するだけです。マルチレベル信号伝送による信号対雑音比(SNR)の低下により、新しいレシーバーは6-Wirestateモードの2倍の感度を有するように仕様化されており、チャネルによるシンボル間干渉(ISI)を補償するため、入力CTLEと組み合わせて使用されることが想定されています。

最新のMIPI C-PHY仕様では、最大シンボルレートが5 Gspsと定義されており、18-Wirestateモードで動作する場合、標準リファレンスチャネル(SRC)の1レーンあたりのデータレートは5 × 3.55 = 17.75 Gbpsとなります。これは、6 Gspsのより高いシンボルレートで動作する場合でも、6-Wirestateモードで実現可能な1レーンあたり6 × 2.28 = 13.68 Gbpsのスループットをはるかに上回っています。ショート・リファレンス・チャネルを考慮すると、性能差はさらに拡大します:18-Wirestateモードでは1レーンあたり最大7 × 3.55 = 24.84 Gbpsを実現する一方、6-Wirestateモードでは8 × 2.28 = 18.24 Gbpsとなります。

MIPI C-PHY 機能の進化の概要

以下の表は、仕様バージョンごとにMIPI C-PHYの主要な機能を要約したものです。

まとめ

要約すると、MIPI D-PHYおよびMIPI C-PHY技術における進歩(Alternate Low Power(ALP)モード、MIPI D-PHYにおけるEmbedded Clockモード、MIPI C-PHYにおける18-Wirestateモードなど)は、先進プロセスノードとの互換性、長距離接続、配線数の削減、EMI放射、データスループットのスケーラビリティといった重要な課題に効果的に対応しています。これらのイノベーションは、既存のインフラの効率的な活用を維持しつつ、後方互換性を保ちながら、より新しい低コストな実装の可能性を拓きます。技術的な環境が進化し続ける中、これらのインターフェイスの向上した性能と柔軟性は、カメラやディスプレイアプリケーション向けの次世代高速通信システムを推進する上で不可欠な役割を果たすでしょう。

MIPI® and MIPI M-PHY® are registered trademarks owned by MIPI Alliance. MIPI C-PHYTM and MIPI D-PHYTM are trademarks of MIPI Alliance.