For more information, contact us here.

The Mixel MIPI M-PHY (MXL-MPHY) is a high-frequency low-power, Physical Layer IP that supports the MIPI® Alliance Standard for M-PHY. (Learn more about Mixel’s MIPI ecosystem at Mixel MIPI Central which gives you access to Mixel’s best of class MIPI ecosystem supply chain partners.) The IP can be used as a physical layer for many applications, connecting flash memory-based storage, cameras and RF subsystems, and for providing chip-to-chip inter-processor communications (IPC).

It supports MIPI UniPro and JEDEC Universal Flash Storage (UFS) standard. By using efficient BURST mode operation with scalable speeds, significant power savings can be obtained. Selection of signal slew rate and amplitude allows reduction of EMI/RFI, while maintaining low bit error rates.

M-PHY Options:

M-PHY HS-G1

M-PHY HS-G2

M-PHY HS-G3

M-PHY HS-G4

The Mixel M-PHY (MXL-MPHY) Features:

- Supports the MIPI Standard for MIPI M-PHY Specification v4.1

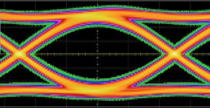

- Dual-simplex point-to-point interface with ultra low voltage differential signaling

- Slew-rate control for EMI reduction

- Supports all HS modes (HS GEAR 1-4, Series A/B)

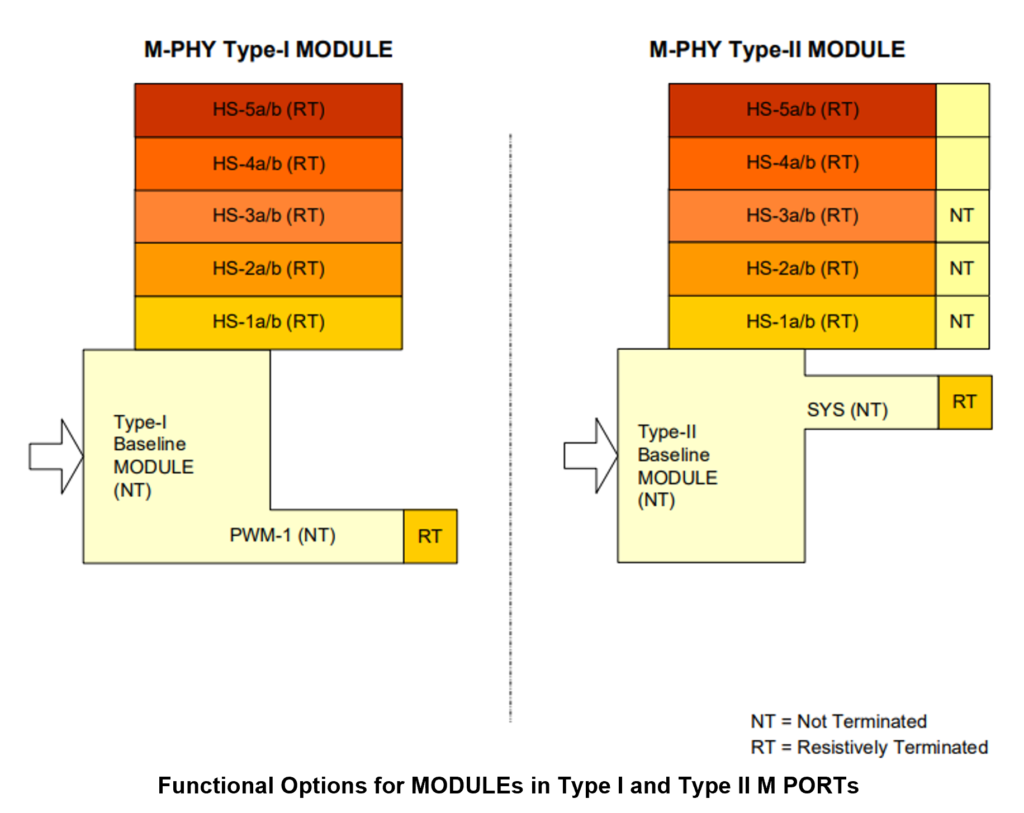

- Supports all Type-I LS modes (PWM GEAR 0-7)

- Supports Type-II LS mode (SYS)

- 1.248-11.6608Gbps data rate in HS mode

- 0.01-576Mbps data rate in LS mode

- Supports (8b10b) symbol encoding and decoding

- Supports the use of optical media converters

- Modular design to allow for all possible configurations

- Designed to be able to operate with independent local reference clocks at each side, but suitable to exploit the benefits of a shared reference clock

- Supports wide range of common reference frequencies

- Low power dissipation

To learn more about Mixel’s silicon-proven IP, please visit Mixel’s contact page or read Mixel MIPI M-PHY related whitepapers here.