次世代VRディスプレイの課題 ―解決のカギはMIPIソリューション

About the Authors:

Ahmed Ella

GM Mixel Egypt, Mixel, Inc.

Jeff Lukanc

Sr. Director, IoT Product Lines, Synaptics

仮想現実(VR)と拡張現実(AR)は長年、ゲームなどのエンターテイメント向けアプリケーションと強く結びつけられてきました。今日、VR / ARとそれらを組み合わせたMixed Reality(MR)は、医療、軍事、教育、製造、小売、マーケティング、広告など様々な分野での適用が模索されています。そこで、次世代VRディスプレイの課題は何なのか? MIPIインターフェースがVR / AR / MRアプリケーションに最適なのはなぜか? 幅広い分野へMIPIソリューションを提供するMixel Inc.は、どのようにMIPI PHY製品を柔軟性の高い独自ソリューションとして実現しているか?これらの質問に対して、このコラムの中で明らかにしていきます。

多様化するアプリケーションやVRのユースケースをサポートし、PC、携帯電話、モバイル機器などからVRディスプレイを駆動するという需要が多くなり、それらに対応するための次世代VRディスプレイは現代のVRディスプレイと比べて多くの点で進歩しています。

第1世代のVRディスプレイは1k x 1kの解像度に対応していましたが、これは高解像度の画像を表示するには不十分でした。次世代のVRディスプレイは、最高のユーザーエクスペリエンスを提供するため、最高で1000kp /インチ(PPI)の解像度に対応し、最小2k x 2k~最大4k x 4kの解像度まで対応するようになっています。

次世代VRディスプレイはより鮮明な画像を表示するために非常に高い応答速度をターゲットにしています。これを達成するための技術の1つは、画素をロードし安定させてから、バックライトを点灯しユーザーに提示します。これを達成するためには、ディスプレイはより速い速度での更新が必要となり、高い帯域幅が必要になります。

もう1つの課題は映像の遅延を短縮させることです。長い映像の遅延は、投影される映像の劣化を発生させ、また映像と音声の同期ズレを引き起こし、VR酔いに繋がります。次世代のVRディスプレイのICsは、遅延が最小になるような最適化が必要になり、低遅延のインターフェースの導入が必要です。

より高い解像度と高いリフレッシュレート、および速い応答速度をサポートするための帯域幅増加は、消費電力に注目せずには実現できません。没入型ヘッドマウントディスプレイに一般的に採用されているVRデバイスは、高いユーザー利便性を提供するため最小限の電力消費に抑える必要があります。また、携帯電話やその他のモバイル機器から駆動されるディスプレイにおいても、消費電力を最小にすることが重要な要件である。MIPI規格はまさにこのようなニーズに応え、消費電力を最小限に抑えながら、広帯域幅、低レーテンシのアプリケーションをサポートするために開発されました。

XRシステムのMIPI

XRという用語は、VR、ARおよびMRのいずれか、あるいはそれらどれかの組み合わせを指すものとして一般的に使われています。ここで、MIPIのC-PHY℠およびD-PHY℠インターフェースはなぜXRアプリケーションに最適なのか、さらにMixel社がどのように回路面積と消費電力を最小限に抑えているかをお話します。

MIPI D-PHYは、1クロックレーンと複数のデータレーンを使用する単純なソース同期PHYです。2009年から使われていて、CSI-2℠とDSI℠のアプリケーションに広く採用されています。一方、C-PHYはMIPIファミリーの新しいメンバーで、D-PHYよりも複雑です。 C-PHYは3つの信号で動作し、クロックはデータに埋め込まれているため、独立したクロックレーンは不要です。シングルレーンのD-PHY 1.2構成では、クロックレーン用のピンが2本、データレーン用のピンが2本の合計4本が必要で、最大2.5 Gbpsのデータレートを達成します。シングルトリオC-PHY 1.1構成では3本のピンのみを必要とし、最大2.5 Gspsのシンボルレートを達成し、5.7 Gbpsに相当します。 MIPI C-PHYの巧妙で効率的なマッピングとエンコード技術のおかげで、データレート効率は2.28倍になります。

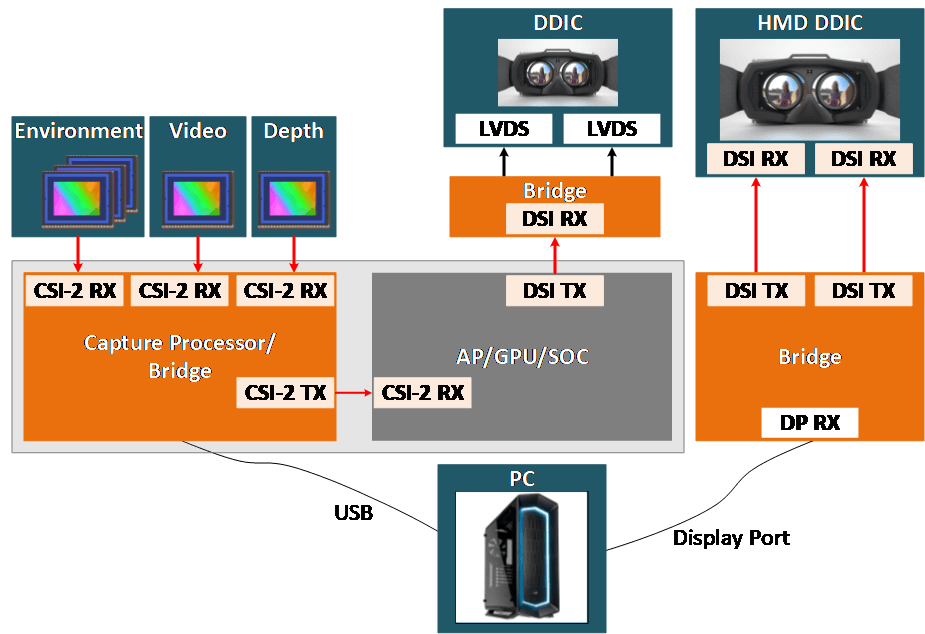

VR、AR、およびMRシステムにおけるMIPI D-PHYとMIPI C-PHYの異なる使用例を説明するために、以下の図1を見てみましょう。

MIPI CSI-2インターフェースは、異なるタイプのセンサ(環境、ビデオキャプチャ、深度センサなど)と反対側のキャプチャプロセッサまたはブリッジチップとの間のインターフェースであり、ARアプリケーションで広く使用されています。 DSIインターフェースは通常、GPUプロセッサがディスプレイを駆動するVRアプリケーションで使用されます。キャプチャプロセッサとメインホストプロセッサの間のインターフェースは、もう1組のMIPI TX / RX低遅延PHYを導入することができます。プロセッサ(携帯電話、デスクトップPC、またはノートPC)でMIPI以外のインタフェースが使用されるアプリケーションでは、ブリッジチップを配置してデータをMIPI形式に変換できます。DSIもCSI-2も、MIPI C-PHYあるいはMPI D-PHY物理層を介してデータを送信することができるMIPIプロトコルとなります。

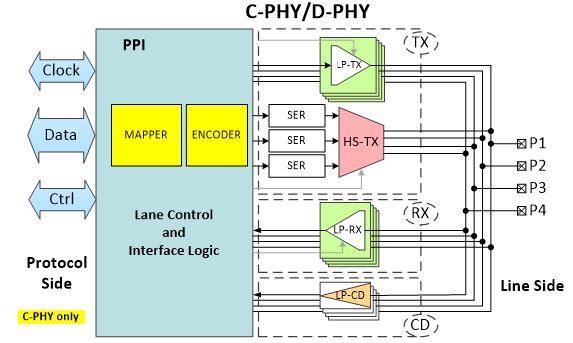

Mixel社のデュアルモードC-PHY / D-PHY (C-PHY / D-PHY Combo)

Mixel社のデュアルモードC-PHY / D-PHY実装は、同じパッドを共有しながら両方を組み合わせたPHYに統合します。 D-PHYリンクはそれぞれ2.5Gbps の1〜4レーンで動作し、C-PHYリンクはそれぞれ最大2.5Gbpsの1〜3レーンで動作します。これは5.7Gbpsに相当します。 Mixel C-PHY / D-PHY Combo は、D-PHYモードで最大10 Gbps、C-PHYモードで17.1 Gbpsの総データレートをサポートします。

Combo PHY IPは、シリアルインターフェースピンを共有するだけでなく、MIPI C-PHY用にすべてのMIPI D-PHY機能ブロックを再利用し、使用していない面積と電力浪費を最小限に抑えます。以下の図2は、最新のVRディスプレイを駆動するように設計されたDSIホストアプリケーション用のMixel MIPI C-PHY / D-PHY Comboのブロック図を示しています。

Mixel C-PHY / D-PHY Comboは、D-PHYモードとC-PHYモードの両方でレーンスワッピングと極性変更の機能をサポートします。このような機能があれば、レーン/トリオを複数の組み合わせに構成できるため、システム統合とPCB配線ははるかにスムーズになります。

また、BIST(Built-in-Self-Test)エンジンを搭載しているため、複数階層(IC、PCBなど)にわたるPHYのテストが可能です。 BISTエンジンは、さまざまなMIPI動作モードで、可観測性と制御性を向上させた状態でCombo PHYをテストできます。製造テストと特性評価テストの両方を可能にするために、さまざまなテストシナリオが実装されています。

Synaptics社のユースケース

Mixel C-PHY / D-PHY Combo TXソリューションを採用するSynaptics Incorporatedは、ハイテクヒューマンインターフェースソリューションの大手プロバイダで、MIPI C-PHYとD-PHYの両方を使用して世界初のディスプレイアプリケーションICを開発しました。 VXR7200 VRブリッジは、VESA DP1.4の全帯域幅を使用するテザーUSB Type-Cケーブル用の接続ソリューションです。 DSC圧縮で最大3k x 3k @ 120Hzの解像度を持つVR、AR、およびMRデュアルディスプレイヘッドセットに最適化され、クラス最高のHMDユーザーエクスペリエンスを実現します。 Synaptics R63455 VRディスプレイドライバICは特別なVRディスプレイタイミングモードを使ってディスプレイを駆動するコンパニオンチップです。

VXR7200 VR Bridgeチップは、ブリッジのDisplayPort側とMIPI側の両方を管理します。 Display Portインターフェースを介してGPUプロセッサと通信し、ビデオフォーマット(Sub-Pixel Render、420、444、8ビット、10ビット)、圧縮設定、フレームタイミングの割り当てなどの表示要件を提供します。一方、Mixel MIPI C-PHY / D-PHY ComboおよびDSI-2コントローラはディスプレイドライバIC(DDIC)と通信してビデオフォーマット、圧縮設定、パネルスキャンタイム、セトリングタイム、バックライトフラッシュタイムなどを設定します。

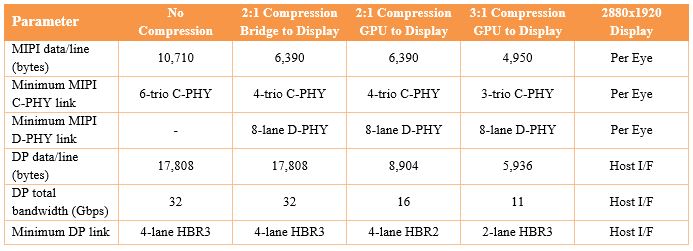

リンクごとに2つのMixel C-PHY / D-PHY ComboおよびDSI-2コントローラを統合することによって、ブリッジチップのMIPIインターフェースは、6つのMIPI C-PHYトリオと同じチップピンを共有する8つのMIPI D-PHYデータチャネルをサポートするように拡張されます。MIPIインターフェースは、さまざまな世代のディスプレイパネル、複数の解像度と帯域幅のオプション、およびさまざまな圧縮設定をサポートするように高度な設定が可能です。以下の表1は、さまざまなアプリケーションと構成をサポートするためになぜC-PHY / D-PHY Comboインターフェースが必要かを説明しています。

上の表は、1眼あたり90Hzの表示で2880×1920を駆動するためのさまざまな構成例を示しています。圧縮なしの場合、DPリンクは32Gbps帯域幅をサポートする4レーンHBR3に、MIPIインターフェース側の6 C-PHYトリオに設定して、1眼あたり2880 x 1920を駆動する必要があります。このユースケースでは、D-PHYの最大サポート帯域幅がそのような構成におけるシステム要件を下回るために使用できず、この重要な機能をサポートするにはC-PHYが必要でした。

ブリッジからディスプレイ、またはGPUからディスプレイへの圧縮が有効になっている場合は、さまざまな構成のD-PHYレーンまたはC-PHYトリオを使用して、最適な消費電力で必要なMIPI帯域幅を提供できます。

シリコンの結果

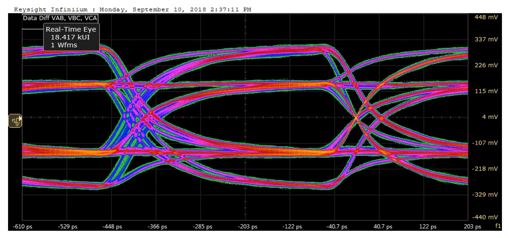

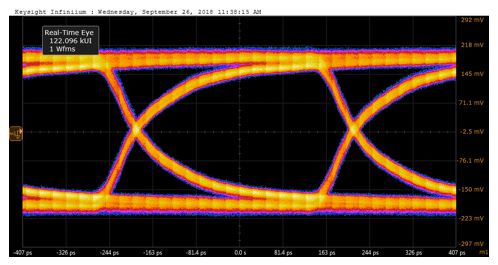

以下は、Synaptics社の VXR7200 VR Bridge ICに統合されたMixel C-PHY / D-PHY Comboのテスト結果を示す2つのスナップショットです。 これはMixel Combo PHY IPとDSI-2コントローラが初のデザインウィンとなり実装され、量産化されて現在市場に出ています。

VR / AR / MRアプリケーションは、最小限の電力消費や遅延、EMIと共により高い帯域幅への対応という需要の増加とともに、さまざまな分野で成長しています。 MIPIインターフェースは、XRアプリケーションの要件に完全に適しており、Mixel社のC-PHY / D-PHY Combo IP製品は、ユニークかつ様々な用途に柔軟に対応できるソリューションです。 Mixel C-PHY / D-PHY製品でサポートされているマルチリンク構成は、すべてのXRディスプレイおよびセンサーアプリケーションに最適です。

この記事を読んだ人はこちらの記事も読んでいます。

MIPI C-PHY / D-PHY サブシステムを解き明かす

携帯電話内部の高速データ転送,次の主役は「MIPI M-PHY」―― 広範なアプリケーションを見据えた多芸多才の標準規格

To learn more about Mixel’s silicon-proven IP, please visit mixel.com/ip-cores or Mixel’s contact page.

Translated by Fujisoft.