双模 C-PHY/D-PHY:支持下一代 VR 显示器

About the Authors:

Ashraf Takla

Founder & CEO, Mixel, Inc.

Jeff Lukanc

Sr. Director, IoT Product Lines, Synaptics

多年来,虚拟现实 (VR) 和增强现实 (AR) 与游戏和娱乐应用密切相关。 如今,VR/AR 及其组合版本混合现实 (MR) 的应用已扩展到其他领域,如医疗保健、军事、教育、制造、零售、营销和广告。 下一代 VR 显示器面临哪些挑战? 是什么让 MIPI® 接口最适合 VR/AR/MR 应用? Mixel, Inc. 如何将不同的 MIPI PHY 产品组合成独特、差异化、灵活的解决方案? 这些问题的答案将在整篇文章中揭晓。

为了支持 VR 的多样化应用和用例,并满足对 PC、手机和便携式设备驱动 VR 显示器不断增长的需求,与当前一代相比,下一代 VR 显示器在许多方面都取得了进步。

第一代 VR 显示器支持 1k x 1k 分辨率,这不足以在近视场显示高分辨率图像。 下一代 VR 显示器的目标是支持约 1000 像素每英寸 (PPI) 的显示分辨率,以实现 2k x 2k 的最低显示分辨率,一直到 4k x 4k,提供最佳用户体验。

下一代 VR 显示器的另一个目标是响应能力,即 LCD 晶体必须在用户观看之前稳定下来,以便在近场视野中呈现清晰的 LCD 图像。 实现这一点的技术之一是加载像素,让它们有一些时间稳定下来,然后闪烁背光,这样用户只能在像素稳定后才能看到它们。 为实现这一点,显示面板必须以更快的速度更新,这意味着更高的带宽要求。

降低视频延迟是另一项挑战。 高视频延迟会导致视频内容滞后,从而导致视频和音频内容不同步。 这种影响会导致晕车问题。 下一代 VR 显示 IC 应针对最低延迟进行优化,这需要部署低延迟接口。

如果在乎功耗的增加,就无法增加带宽以支持更高分辨率、更高刷新率和更快的响应速度。 通常部署在沉浸式头戴式显示器中,VR 设备应该消耗最小的功率,从而产生的热量可以忽略不计,以提供方便的用户体验。在显示器由手机或其他便携式设备驱动的应用中,最小化功耗仍然是关键要求。虽然所有标准化接口都在竞相实现最高带宽,但 MIPI 规范是从头开始开发的,以支持高带宽、低延迟应用程序,同时最大限度地降低功耗。

XR 系统中的 MIPI

术语 XR 通常用于指代任何现实技术 VR、AR 和 MR 或其任意组合。 现在,让我们快速浏览一下 MIPI C-PHYSM 和 D-PHYSM 接口,解释为什么它们是 XR 应用的最佳选择,以及 Mixel 如何以最小的面积和功率开销在单个 PHY 中结合这两种接口的特性。

MIPI D-PHY 是一种简单的源同步 PHY,它使用一个时钟通道和不同数量的数据通道。 它自 2009 年以来一直存在,并广泛部署在 CSI-2SM 和 DSISM 应用程序中。 另一方面,C-PHY 是 MIPI 家族的新成员,也是更复杂的 PHY。 C-PHY 在三个信号上运行,一个三重奏,时钟嵌入到数据中,因此不需要单独的时钟通道。 单通道 D-PHY 1.2 配置需要四个引脚,两个引脚用于时钟通道,两个引脚用于数据通道,实现高达 2.5 Gbps 的数据速率。 单三重 C-PHY 1.1 配置仅需要三个引脚,可实现高达 2.5 Gsps 的符号率,即 5.7 Gbps。 得益于 MIPI C-PHY 巧妙而高效的映射和编码技术,数据速率效率提高了 2.28 倍。

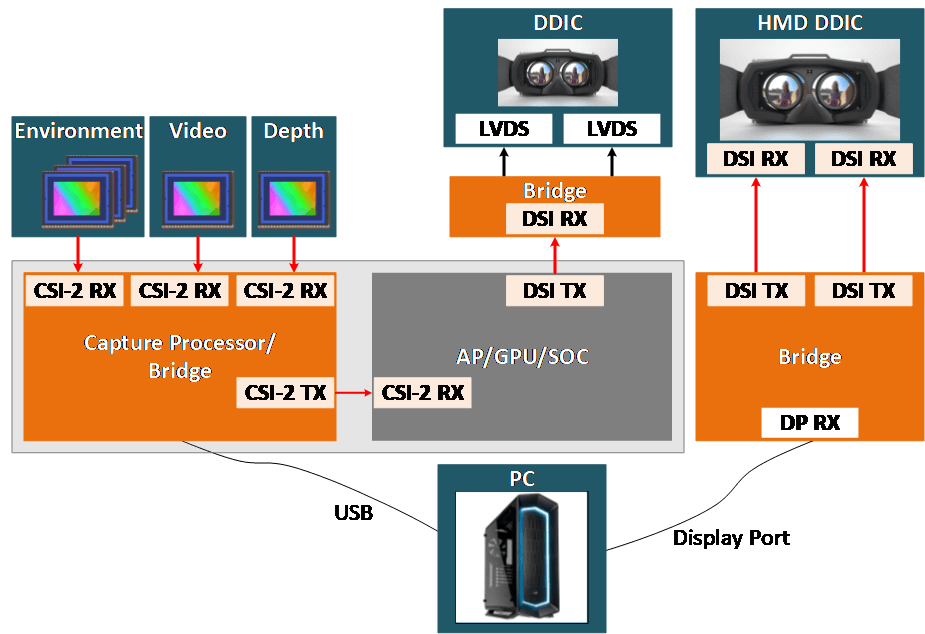

为了解释 MIPI D-PHY 和 MIPI C-PHY 在 VR、AR 和 MR 系统中的不同用例,让我们看一下图 1。

MIPI CSI-2 接口通常用于 AR 应用,作为一侧不同类型传感器(环境、视频捕捉、深度捕捉)与另一侧捕捉处理器或桥接芯片之间的接口。 DSI 接口通常用于 VR 应用程序,其中 GPU 处理器将驱动显示面板。 捕获处理器和主机处理器之间的接口可以部署另一对 MIPI TX/RX 低延迟 PHY。 在系留应用中,处理器(手机、台式机或笔记本电脑)使用非 MIPI 接口,可以部署桥接芯片将数据转换为 MIPI 形式。 DSI 和 CSI-2 都是 MIPI 协议,可以通过 MIPI C-PHY 和/或 MIPI D-PHY 物理层发送数据。

Mixel 的双模 C-PHY/D-PHY

Mixel 的双模式 C-PHY/D-PHY 实现将两者组合成一个组合 PHY,同时共享相同的管脚盘。 D-PHY 链路可以作为 1 到 4 条通道运行,每条通道以 2.5Gbps 运行,而 C-PHY 链路可以作为 1 到 3 条通道运行,每条通道以高达 2.5Gbsps 的速度运行,相当于 5.7Gbps。 Mixel Combo PHY 在 D-PHY 模式下支持高达 10 Gbps 的聚合数据速率,在 C-PHY 模式下支持高达 17.1Gbps 的聚合数据速率。

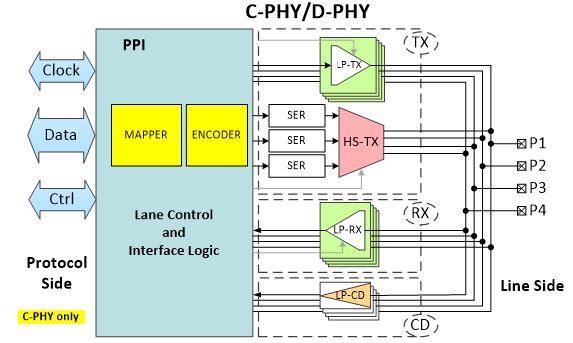

Combo PHY IP 不仅共享串行接口引脚,而且 Mixel 的实现还为 MIPI C-PHY 重用了所有 MIPI D-PHY 功能块,从而最大限度地减少了管芯面积和泄漏功率。 下面的图 2 显示了 Mixel MIPI C-PHY/D-PHY Combo TX 的框图,用于 DSI 主机应用,旨在驱动最新的 VR 显示器。

Mixel Combo C-PHY/D-PHY 支持 D-PHY 和 C-PHY 模式下的通道交换和极性更改功能。 有了这样的功能,系统集成和 PCB 布线就会更加顺畅,因为通道/三重奏可以配置为多种组合。

它还配备了内置自测试 (BIST) 引擎,可以跨多个抽象层(IC、PCB 等)测试 PHY。 BIST 引擎能够在不同的 MIPI 操作模式下测试 Combo PHY,并提高可观察性和可控性。 实施了各种测试场景以支持生产和特性测试。

Synaptics 的用例

部署 Mixel C-PHY/D-PHY 组合 TX 解决方案,领先的高科技人机界面解决方案提供商 Synaptics Incorporated 开发了世界上第一款同时使用 MIPI C-PHY 和 D-PHY 的显示应用 IC。 VXR7200 VR Bridge 是一种连接解决方案,适用于部署完整 VESA DP1.4 带宽的系留 USB Type-C 电缆。 它针对分辨率高达 3k x 3k @ 120Hz 的 VR、AR 和 MR 双显示器耳机进行了优化,具有 DSC 压缩功能,可实现一流的 HMD 用户体验。 Synaptics R63455 VR 显示驱动器 IC 是一款配套芯片,可使用特殊的 VR 显示时序模式驱动显示器。

VXR7200 VR 桥芯片管理桥的 DisplayPort 和 MIPI 端。 它通过显示端口接口与 GPU 处理器通信,以提供显示要求,如视频格式(子像素渲染、420、444、8 位、10 位)、压缩设置和帧时序分配。 另一方面,Mixel MIPI C-PHY/D-PHY 和 DSI-2 控制器用于与显示驱动器 IC (DDIC) 通信以配置视频格式、压缩设置、面板扫描时间、建立时间、背光闪烁时间和 局部调光设置。

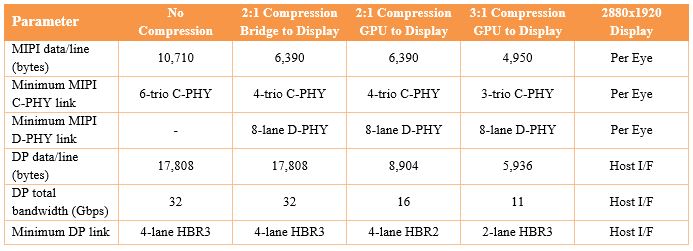

通过在每个链路上集成两个 Mixel Combo C-PHY/D-PHY 实例和 DSI-2 控制器,桥接芯片 MIPI 接口扩展为支持八个 MIPI D-PHY 数据通道,与六个 MIPI C-PHY 三重奏共享相同的芯片引脚 每只眼睛。 桥接 MIPI 接口具有高度可配置性,可支持不同代的显示面板、多种分辨率和带宽选项以及不同的压缩设置。 下面的表 1 解释了为什么需要双模 C-PHY/D-PHY 接口来支持各种应用和配置。

上表显示了每只眼睛以 90Hz 显示器驱动 2880×1920 显示器的不同配置示例。 在没有压缩的情况下,DP 链路必须配置为支持 32Gbps 带宽的 4 通道 HBR3,这必须与 MIPI 接口侧的 6 个 C-PHY 三重奏相匹配,以驱动 2880×1920 每眼显示器。 D-PHY 不能用于此,因为它支持的最大带宽低于此类配置中的系统要求。 需要 C-PHY 支持才能支持此重要功能。

当启用桥接显示或 GPU 显示压缩时,可以使用 D-PHY 通道或 C-PHY 三重奏的不同配置,以优化功耗提供所需的 MIPI 带宽。

硅结果

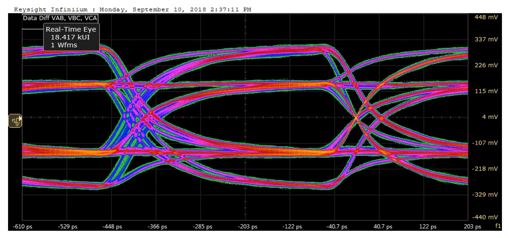

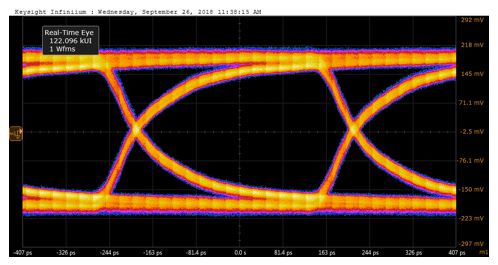

以下两张快照显示了集成到 Synaptics VXR7200 VR Bridge IC 中的 Mixel 双模 C-PHY/D-PHY 的测试结果。 VXR7200 桥接芯片通过 Mixel Combo PHY IP 和 DSI-2 控制器首次在硅片上取得成功,现已投入生产,现已上市。

总而言之,VR/AR/MR 应用在不同领域不断发展壮大,对以最低功耗、延迟和 EMI 支持更高带宽的需求不断增加。 MIPI 接口属性非常适合 XR 应用程序要求。 Mixel 双模 C-PHY/D-PHY IP 产品是适用于系统启动和应用用例的独特、灵活和通用的解决方案。 Mixel C-PHY/D-PHY 产品支持的多链路配置使其成为所有 XR 显示器和传感器应用的理想选择。

相关文章

To learn more about Mixel’s silicon-proven IP, please visit mixel.com/ip-cores or Mixel’s contact page.