The MXL-LVDS-MIPI-RX is a high-frequency, low-power, low-cost, source-synchronous, Physical Layer that supports the MIPI® Alliance Standard for D-PHY and compatible with the TIA/EIA-644 LVDS standard. (Learn more about Mixel’s MIPI ecosystem at Mixel MIPI Central which gives you access to Mixel’s best of class MIPI ecosystem supply chain partners.)

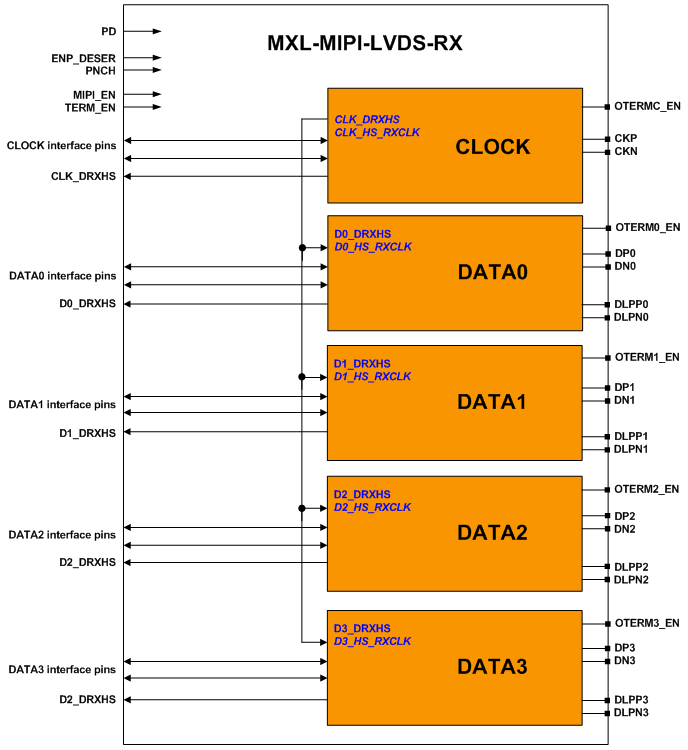

The IP is configured as a MIPI slave and consists of 5 lanes: 1 Clock lane and 4 data lanes, which make it suitable for display serial interface applications (DSI).

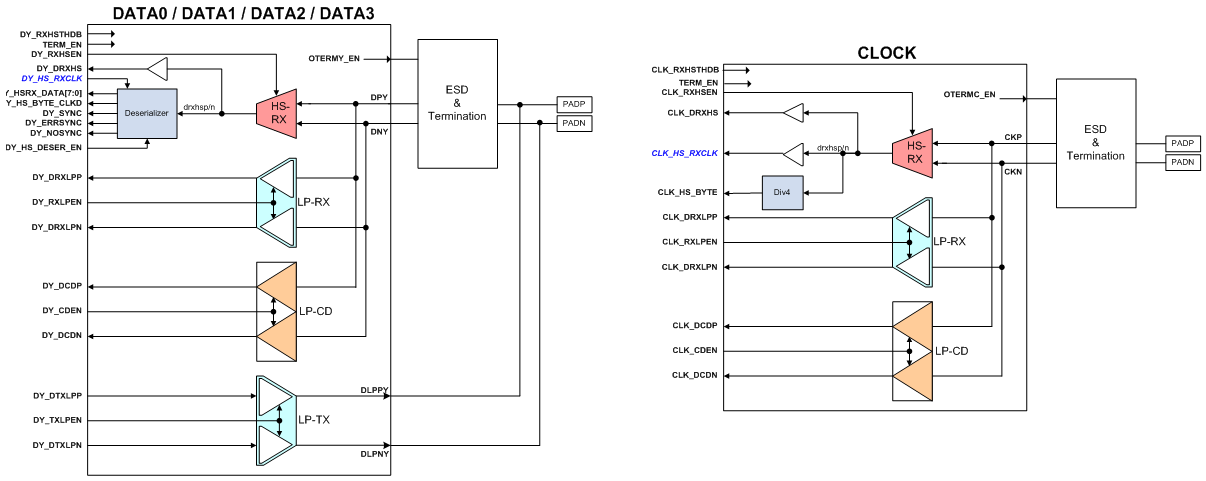

The High-Speed signals have a low voltage swing, while Low-Power signals have large swing. High-Speed functions are used for High-Speed Data traffic while low power functions are mostly used for control.

LVDS/D-PHY Comparable Receiver Features:

- Consists of 1 Clock lane and 4 Data lanes

- Up to 4.0 Gbps data throughput

- Supports the MIPI Standard 1.0 for D-PHY

- Compatible with TIA/EIA-644 LVDS standard

- Supports both high speed and low-power modes

- 80 Mbps to 1 Gbps data rate in MIPI high speed mode

- 140 Mbps to 945 Mbps data rate in LVDS high speed mode

- 10 Mbps data rate in low-power mode

- High Speed De-Serializers included

- Low power CMOS design

- Power down mode

- 1.2V/3.3V dual power supply

Mixel’s Production Ready Offering (“PRO IP”): LVDS/D-PHY Combo Receiver

| LVDS/D-PHY CSI-2 RX Combo (4CH/4L, 600Mbps/1.5Gbps) in TSMC 28HPC+ | More information |