MIPI D-PHY 和 C-PHY的前沿技术探索

作者:

Michael Nagib

AMS 总监, Mixel, Inc.

Nuno Martins

总经理, Xpressphy

引言

在日新月异的高性能摄像和显示技术领域,MIPI D-PHY™ 和 MIPI C-PHY™ 规范持续引领潮流,为低功耗、低延迟和高带宽数据传输建立了标杆。基于我们之前文章《解读MIPI C-PHY D-PHY子系统》的见解,我们现在将深入探讨这些规范的最新进展及其在视觉和成像技术领域变革的潜力。

推动技术创新的市场驱动力

当 MIPI D-PHY 在 15 多年前推出时,其主要关注点是为移动市场创建一个简单、低功耗且中频带宽的接口。2014 年,MIPI C-PHY的推出在更高损耗通道上为系统设计者提供了实现更高能效接口的解决方案,尽管引入了额外的设计复杂度。

自那时起,随着图像动态范围、像素分辨率和帧率的提升,行业对摄像头和显示器的数据速率需求呈现爆发式增长。这些提升不仅对改善用户视觉体验至关重要,而且对实现实时高级图像处理也必不可少。因此,为应对持续增长的市场需求,MIPI D-PHY与C-PHY接口通过版本迭代实现数据速率的持续提升,这一技术演进路径已成为行业共识。

最近,这些接口已扩展到移动市场之外,使企业能够利用芯片设计、软件开发和测试基础设施方面的规模经济效应和投资。目前MIPI D-PHY 和 MIPI C-PHY 已应用于汽车(信息娱乐系统、高级驾驶辅助系统、自动驾驶)、工业(机器视觉、机器人、监控)、沉浸式头显(增强现实/AR、虚拟现实/VR、混合现实/MR)、医疗保健以及其他领域。如此广泛的应用范围正在推动接口的迭代,更加关注减少功耗、更长传输距离能力、减少引脚数量等方面。

在这些新市场中的部署也给 IP 和 IC 供应商带来了显著区别于移动应用端的技术挑战。例如,汽车电子的安全关键型应用要求芯片设计具备更高的sigma容差,集成实时故障检测与纠错机制,并能在-40℃至150℃的温度范围内稳定运行,同时通过加速老化测试来确保10-15年的使用寿命。这些严苛的技术规范由ISO 26262功能安全标准和AEC-Q100汽车级IC测试标准体系进行约束。此外,供应商还需考虑电磁兼容性 (EMC),以防止高速数据链路对其他电子系统造成干扰。

通过持续关注所有这些市场力量并相应调整接口,MIPI D-PHY 和 MIPI C-PHY 在我们迈入 6G、人工智能 (AI) 和物联网 (IoT) 等技术发展的新时代时,仍能与时俱进。

MIPI D-PHY 的最新特性

作为 MIPI® 短距离物理接口家族中的“老大哥”,MIPI D-PHY 于 2009 年推出并立即获得成功。它为移动应用中的摄像头和显示器建立了高性能、低成本连接的基础框架。该接口的基本原理在标准的早期版本中基本保持不变。它保持了其双倍数据率同步动态随机存储器 (DDR) 的本质,具有高速 (HS) 模式(使用 SLVS 差分信号进行高吞吐量数据通信)和低功耗 (LP) 模式(使用 Spaced-One-Hot LVCMOS 信号进行控制)。

数据速率提升

在更高带宽需求持续增长的驱动下,新版规范的核心升级方向在于提升每根数据通道的最大传输速率——从 MIPI D-PHY v1.2 的 2500 Mbps 到 v2.x 的 4500 Mbps,最终在 v3.x 中标准信号通道达到 9 Gbps。对于更短的通道长度,甚至可以实现更高的速率,自v3.0版本起支持最高可达11 Gbps的传输速率。通常由于产品形态尺寸及需克服的物理距离基本保持不变,物理信道特性也维持不变。为此,规范引入了信号均衡技术,在支持数据传输速率提升的同时,缓解了高速传输下固有的更高信号损耗与失真问题。

均衡选项

在 MIPI D-PHY v2.0 中,首次以信号去加重 (de-emphasis) 的形式定义发射器均衡技术,对于超过 2.5 Gbps 的速率,能够将高低频信号比增益提高 3.5 dB 或 7 dB。在 v3.0 中,随着速率提升至 9-11 Gbps,接收器端新增连续时间线性均衡器 (CTLE),以进一步增强整体信道的均衡性能。通常结合使用 TX 去加重和 RX CTLE 来平坦化通道的整体频率响应,其优化范围包括内部互连,封装和硅收发器的寄生负载。

随着最新的 MIPI D-PHY v3.5 的推出,在接收器中引入了非线性判决反馈均衡器 (DFE) 技术, 尤其在6 Gbps以上传输速率场景下采用此类技术更具效益。此外,该标准允许在符合早期版本规范的设计中使用上述任何均衡技术,也允许向后续版本兼容,保留了方案实施的灵活性。

低功耗特性

全新的低功耗特性的引入得以提升信号每比特能效,在适配先进硅工艺技术的同时,可以有效应对如今的设计挑战,这些特性包括:

- 半摆幅模式 (Half-swing mode):高速发射器信号幅度减半,特别适用于低速、短距离的互连场景。

- 接收器端接禁用模式 (RX unterminated mode):禁用接收器端的 100 Ω端接阻抗需要配合发射器端半摆幅模式启用)。

- 低压低功耗模式 (Low Voltage Low Power, LVLP mode):低功耗 LVCMOS 发射器信号幅度相较于标压 1.2V 值降低,以更好适配先进 CMOS 工艺制程的核心供电电压。

当 MIPI D-PHY 最初采用 1.2V LVCMOS 信号时,可适配当时多数的硅工艺制程。随着更先进工艺节点的出现,一些问题开始显现。(1)先进制程的核心供电电压远低于1.2V(如5nm制程低至0.75V),需由I/O电源域进行电压转换,引入额外设计负担。(2)1.2V 信号可能对先进制程中的核心器件施加过应力,增加 IO 泄漏电流并缩短器件寿命。(3)如此高电平的轨到轨信号传输严重限制相应的通道长度。(4)1.2V 信号在发射器和接收器两侧都需要特定的电路架构支持,由于焊盘输出负载的增加将导致最大传输速率降低。

LVLP mode作为过渡性特性,允许 LVCMOS 信号电平降至 0.95V 来解决部分问题。然而进一步降低电压,将无法正确区分 HS 和 LP 信号电平的前提下。为了应对这些挑战,MIPI D-PHY v2.5 引入了一种新的操作模式,称为交替低功耗 (Alternate Low-Power, ALP) 模式。在此模式下,不再使用 LP 信号及其相应电路,而是通过原本用于高速通信的 HS 发射器(HS-TX)和 HS 接收器(HS-RX)电路来实现。通过使用与高速模式相似的信号电平,抑制过量漏电并提升在先进制程中的适配性、可靠性,同时支持在长达四米的物联网信道上传输。

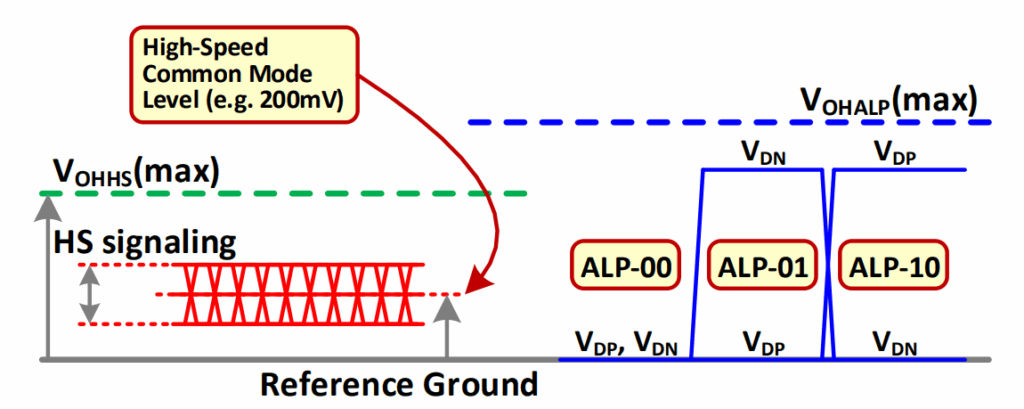

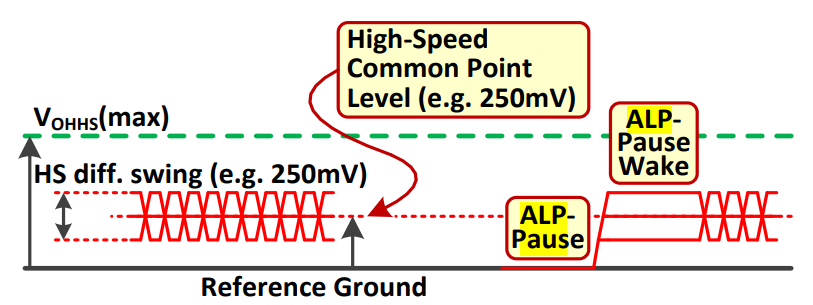

尽管在 ALP 模式下采用了 HS-TX ,但特别之处在于HS-RX 在 ALP 期间会处于未端接状态以降低功耗,并且信号电平并不总是差分传输的。如下图所示,存在一种 ALP-00 状态,其中两条信号同时接地。

ALP-00 直接取代了传统的 LP Stop 和 ULPS 状态由发射器主动驱动,将两条传输线路接地达到塌陷差分状态(collapsed differential state),其共模电压与差分摆幅均为零,这是在长时间空闲期间降低功耗的关键。

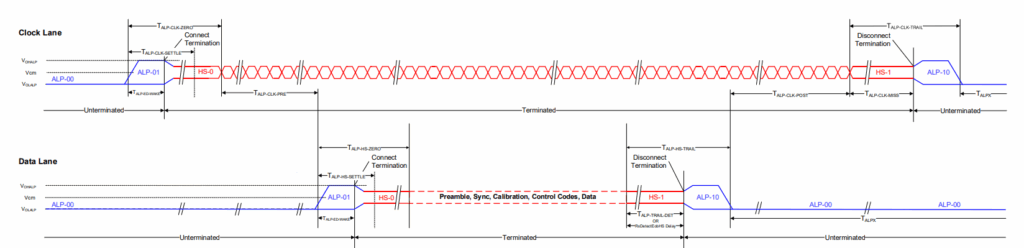

图 2 展示一种常见的ALP跳变状态(以一个时钟通道和一个典型的数据通道为例)。两个通道都从 ALP 停止状态 (ALP-00) 开始并可保持长时间空闲状态。当数据或控制信号准备好传输时,时钟通道首先通过发送唤醒脉冲信号激活ALP-01,待高速时钟稳定后,数据通道随后发送类似的唤醒脉冲信号。接收器端使用ALP退出检测器 (ALP-ED) 识别 ALP-01 唤醒脉冲,之后启用差分端接为高速通信(包括数据、控制代码、校准模式等)做准备。

通信以传输一个长的 HS 尾部序列 (HS-Trail sequence) (HS-1/ALP10) 结束,并转换回 ALP 停止状态,数据通道先切换,然后是时钟通道。每个通道上的接收器在检测到 HS 尾部序列后禁用端接。此流程可根据数据传输或控制触发需求重复执行。

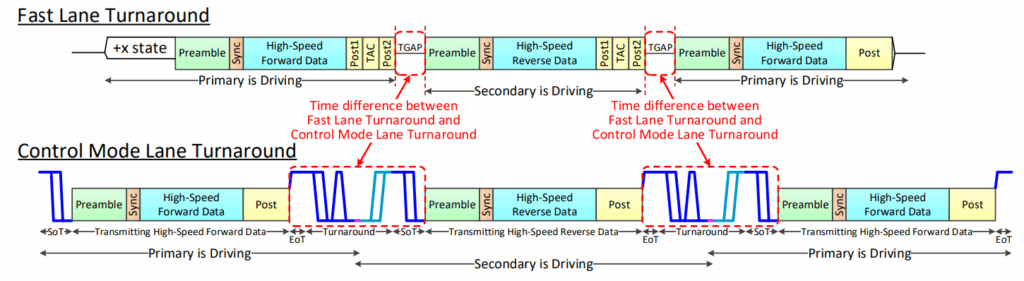

相较于传统模式,ALP的另一关键优势在于能够显著降低双向通道模块的通道切换时间(lane turnaround time)。在传统 LP 模式下,通道切换依赖于一个持续时间为 50ns 不随高速数据速率而变化的固定低功耗状态信号。ALP 引入了快速通道切换 (Fast Lane Turnaround) 的概念,使用16单位间隔控制码(16UI control code) 实现时序优化。在 1Gbps 速率下,切换时间比传统 LP 模式减少约一半,在更高传输速率下将进一步减少。该机制有效地将切换时间从传统 LP 模式的 1us 减少至 ALP 模式的几百纳秒。

快速通道切换和 ALP 特性的协同为 MIPI CSI-2®(摄像串行接口)创造了新型应用模型,实现统一串行链路 (Unified Serial Link, USL) 架构,允许数据通信和边带摄像控制接口 (Camera Control Interface, CCI) 共用同一个高速链路传输,减少了线缆数量并扩展了通道距离。

针对转接时钟的MIPI D-PHY 因持续反转时钟容易产生更高的 EMI,除了通过系统级屏蔽缓解这一问题之外, MIPI D-PHY 从 2.0 版本开始引入了扩频技术。该技术中,时钟源频率采用三角波triangular profile进行调制,将信号能量分散到更宽的频带,从而降低单频点峰值辐射,规范要求峰值偏差为 -5000ppm,调制速率在 30 至 33KHz 之间。

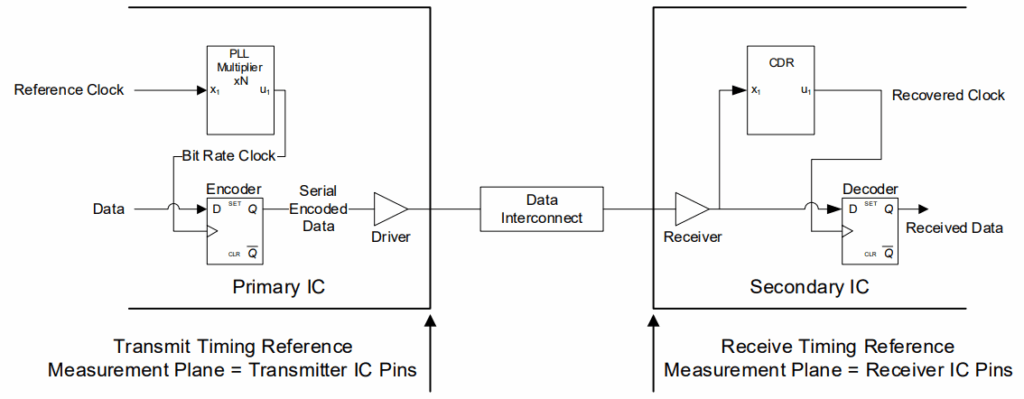

嵌入式时钟模式

2023 年 5 月推出的MIPI D-PHY v3.5 ,引入了新的嵌入式时钟模式 (Embedded Clock Mode, ECM),标志着 D-PHY 架构的重大变革。 在保留前向时钟模式(Forwarded Clock Mode, FCM) 以确保兼容性的同时, ECM 将时钟信息嵌入数据流中并通过接收器端的时钟数据恢复 (Clock and Data Recovery, CDR) 模块进行恢复。此举带来了多项好处:

- 减少 EMI 辐射:去除时钟通道降低电磁干扰。

- 放宽偏移对齐要求:通道之间的时序实现相互独立。

- 减少线缆数量:最小配置可缩减至 2 个引脚。

- 增加数据吞吐量:在典型10引脚配置(4数据+1时钟)下,时钟通道转为数据通道可使总吞吐量提升25%(单通道传输速率不变)。

鉴于初始 MIPI D-PHY 操作框架发生了根本性改变,需深入探讨ECM 模式与 FCM 模式共存机制,两种模式在 MIPI D-PHY v3.5 中均为可选并共享相同的互连结构和电气特性,代表单个 PHY 均可以支持 FCM、ECM 或两者均支持。然而MIPI D-PHY v3.5成为首个不绝对保证主/从设备后向兼容性的版本——仅支持 ECM的新 v3.5 PHY将无法兼容旧的 v1.x-v3.0 PHY ,且双模式PHY在初始化时选定单一模式后,运行期间禁止动态切换。

从FCM模式向ECM模式的转变伴随着部分旧功能的淘汰或不再支持,包括:

- 高速双向传输

- 交替低功耗 (ALP) 模式

- 偏移校准和 FCM 传统前导码序列

为了将时钟时序信息嵌入数据流,MIPI D-PHY ECM 采用了 128b/132b 线路编码(兼容行业标准)并加入干扰机制。每个 132 位数据在链路上进行从左至右串行传输,结构由 4 位header和 128 位数据组成。Header使用 4’b0011 表示控制信号,4’b1100 表示数据信号,提供 1 位冗余纠错能力,编码开销为 3.125%。

协议数据使用多项式 G(x)=x23 + x21 + x16 + x8 + x6 + x2 + 1 和seed 0x1DBFBC 进行加扰,该值在发送数据包起始码 (Start of Packet, STP)时复位。为补足 128 位有效数据位,缺少的协议数据将用0填充。

控制数据不加扰,32 位控制字被复制四次(两次反相,两次非反相)以补足 128 位有效数据位,同时保证DC平衡和容错性。

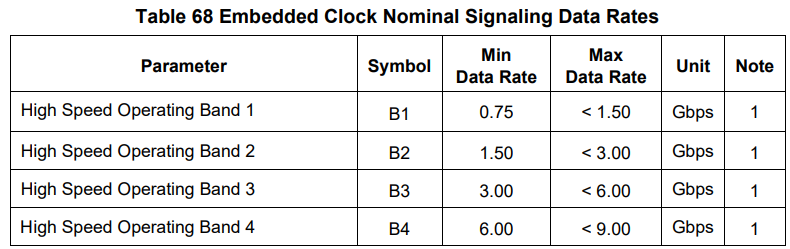

为了避免增加 PHY-协议的成本的基于档位 (gear-based) 接口,D-PHY ECM 定义了一种基于频带 (band-based) 的接口,支持四种工作频带。传感器/显示器 PHY 可选择实现单个频带,而应用处理器 (Application Processor, AP) PHY 必须实现其所支持最高频段内的所有频段。发射器只需要在选定的频带内支持一种数据速率,而接收器必须在支持的频带内适应所有速率。这些约束关系确保了互联性,同时降低了系统的整体成本。

由于接口的频带特性,可以在每个从次级 (Secondary) PHY 单元中使用无参考时钟的 CDR模块,该模块能将输入数据流锁定在四个预设频带之一,其重要意义在于无需预先编码设定次级IC物理层的具体工作速率,从而降低了对锁相环设计的要求。并且它消除了对本地晶振参考源的需求,大幅简化了整体设计并降低了成本。

图 7 展示了一个通用的 ECM 触发场景,保留了 FCM 的诸多特性和时序。LP 部分保持不变,最显著的变化发生在 HS 部分。STP(起始符)和 EDP(结束符)用于界定编码数据,初始化训练序列 (INIT-TRAIN sequence) 用于接收器中的 CDR,初始化训练序列是 1010…交替,若考虑EMI可以选择使用 PRBS9伪随机序列,其持续时间可编程为短序列或长序列,具体取决于自上次信号跳变以来的累积时钟漂移量(规定不超过 25000ppm)。与 FCM 相同,该过程没有数据节流,因此 PHY 在高速模式下连续传输协议数据或控制码,仅在长时间无数据传输时转换到 LP-11。由于训练序列相当长(数千个 UIs),在传统 FCM 中那样频繁的进行 LP-HS-LP 转换已不太实际。因此,该接口在高速模式持续运行,当无有效数据传输时,协议层会插入填充/空闲码维持链路同步传输。

ECM通过将时钟时序嵌入数据流中, 显著提升了系统性能并简化了设计要求,使得 D-PHY 成为一个稳健且适应性强的解决方案。

MIPI D-PHY 特性演进总结

下表总结了各规格版本 D-PHY 的主要特性。

MIPI C-PHY 的最新特性

自MIPI C-PHY v1.0发布十余年来,持续发展提升其工作速率,但受限于其多相位/多电平编码特性(历史上每symbol容纳约2.28比特),其symbol rate提升幅度小于MIPI D-PHY。然而在相同引脚数接口下,C-PHY的总带宽始终大于D-PHY。

Symbol Rate与均衡特性

从初始 2.5 Gsps * 2.28 = 5.7 Gbps 的通道速率,MIPI C-PHY 在 v1.1 和 v1.2 版本中通过不同的发射端均衡方案和特殊的训练序列来微调接收器分别将速率提升到 2.8 Gsps 和 3.5 Gsps。2.x 版本通过增加接收器端的 CTLE使Symbol Rate在标准信道中提高至 6 Gsps(~ 13.7Gbps/通道)。

低功耗特性

在低功耗方面,MIPI C-PHY 与 MIPI D-PHY 基本一致。在 v1.1 中低速运行下接收器允许无需端接。从 v1.2 开始,新增低压高速 (Low Voltage High Speed, LVHS) 模式以降低共模和差分信号摆幅以更好地匹配 MIPI D-PHY 电平(对于组合实现尤其重要),新增低压低功耗 (LVLP) 模式降低 LVCMOS 电平,以及最终的交替低功耗 (ALP) 模式。

MIPI C-PHY 中的 ALP 模式解决了之前 MIPI D-PHY 描述的相同功耗问题,但其解决方案有所不同,它利用了 MIPI C-PHY 的保留字 (reserved words) 触发信号传输。其电平配置如图 9 所示。与 MIPI D-PHY 相似之处在于采用 ALP-Pause 和 ALP Wake脉冲,但关键差异在于ALP Pause 仅要求 VA=VB=VC( AB、BC、CA 差分对信号为0),但不一定像在 MIPI D-PHY 中均接地。唤醒状态通常是 +X态,其中 A 为高电平,B 为低电平,使得 VAB = Vod_strong ,而 C 处于中间电平。

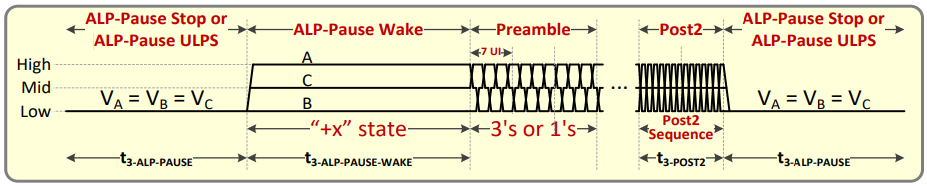

图 10 展示了由三根信号线(A, B, C)组成的单通道的通用 ALP 跳变状态。该通道以 ALP-Pause Stop(或 ULPS)待机状态开始,类似于传统的 LP 模式,但使用如前所述的不同信号电平。而后跳变至ALP-Pause Wake状态传输长时间的 +X 态并唤醒远端接收器,接收器通常会使用低功耗检测器来观察线路状态。与 MIPI D-PHY 不同,在 MIPI C-PHY ALP 模式下接收器端端接没有进行动态切换,因此高/低电平在整个状态跳变期间电压幅值保持一致。

在 +X 态唤醒之后,根据传输的是 ALP 数据/控制或校准信号,将发送全 1 或全 3 的前导码 (Preamble),并最终都会以7UI的停止码(或ULPS码)及可编程长度的POST2字段作为结束序列,示意接收器链路即将返回至待机状态。此序列提供足够的尾随时钟边沿确保数据传输到协议层。

在此期间,高速数据或代表某些特定功能的预留符号序列被发送到链路对端,其中一个预留序列是切换码 (Turnaround Code, TAC),该码触发快速通道跳变(Fast Lane Turnaround)流程,主设备 (Primary) 停止发送数据并转为接收状态,而从设备 (Secondary) 转为互补状态。此过程具有与 MIPI D-PHY 中类似的优势,特别是与较长 LP 状态持续时间的传统 LP 控制模式切换相比降低了状态跳变延迟。

与需要专用跳变控制的 MIPI D-PHY 过程不同,MIPI C-PHY 利用其编码结构将 TAC 码嵌入到原始方向传输的最后一个数据中,进一步减少反向传输所需的时间。下图 11 比较了 ALP 模式与传统 LP 模式下的切换过程。

数据速率提升(18 线状态)

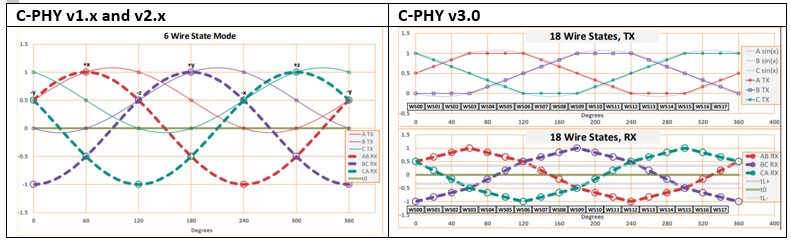

随着对增加带宽的需求持续增长,MIPI C-PHY v3.0 于 2025 年 3 月发布,采用的崭新架构,基于原始 6 线态扩展到 18 线态。这一变化旨在保持或略微降低符号速率的同时提高 MIPI C-PHY 的比特率,尽管架构发生了根本性转变,但仍可兼容旧版本的 6 相位模式。

那么,这个新架构是什么样的?比特率的提升是如何实现的?它能否与旧架构采用类似方案优化工艺成本?让我们通过比较 6 线态和 18 线态解决方案来探讨这些问题。

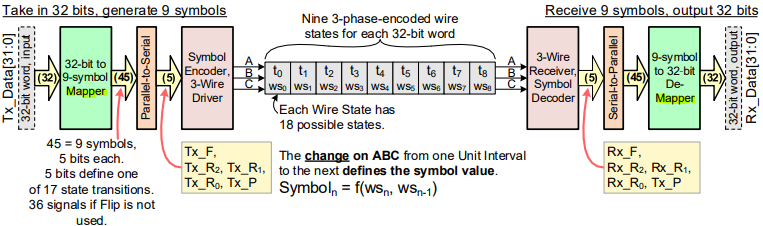

早期版本的 MIPI C-PHY 将来自控制器的 16 位数据映射为一组 7 个符号,实现 16/7 = 2.28x 的编码增益。使用六种线态(+X, -X, +Y, -Y, +Z, -Z)进行编码,三线组 (trio) 中的每条线采用三种可能的电平(高、中、低)之一。

为了在保持相同符号速率的同时提升比特率,新的 18 线态模式将来自控制器的 32 位数据映射为一组 9 个符号,实现 32/9 = 3.55x 的编码增益。接口的物理资源没有增加,意味着每个通道仍然使用相同的三根线(三线组)。然而这些信号线现在采用七种可能的信号电平,为 AB、BC 和 CA 差分对创建了 18 种独特的电平组合(WS0…WS17)。

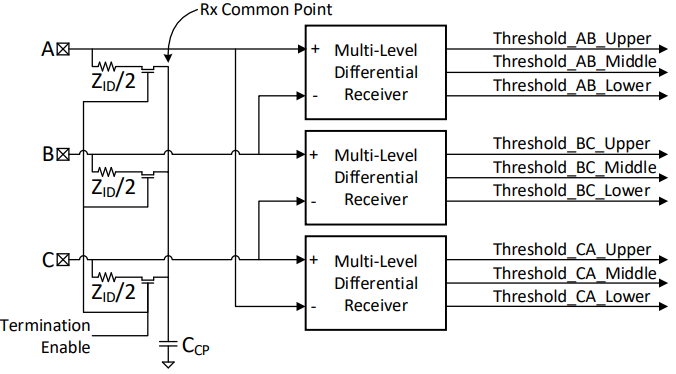

图 12 说明了两种方案相位的差异。在 6 线态模式下,符号检测只需要确定 AB、BC 和 CA 信号对的正负极性。而在 18 线态模式下,除信号对的正负极性之外,还需要与两个额外的电压阈值 (tL+ 和 tL-) 进行比较以明确识别每个状态,每对信号线上的接收器实际上是多电平判决器 (slicer)来确定信号为四种输出之一。

为了确保每个符号至少有一个边沿跳变,MIPI C-PHY协议约束信号在线态间持续转换,总共 17 种跳变组合。将 32 位比特数据映射到线路符号至少需要 232 ≈ 4.295×109 种组合,而9 个符号中的每一个提供 17 种组合,总共产生 179 种不同组合,远远超过最低需求。实际使用中MIPI C-PHY v3.0 限制了某些符号组合的使用以减少抖动并压缩内部数据路径的宽度,使得符号组合成为一个 12 进制编码, 129 ≈ 5.15×109 种组合仍然足以编码所有可能的 32 位比特数据组合。

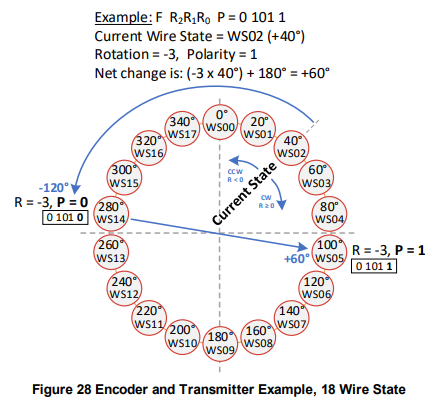

32 位比特数据与 9 个符号之间的转换通过映射函数实现,每个符号由5比特编码表示(取值范围:5’b00000至5’b10000,共17种二进制值)。每比特对应于一个信号线状态变化,包含翻转、旋转、极性(F, R2, R1, R0, P),类似于 6 线态模式:

- 极性 (Polarity, lsb):保持线态极性 (1’b0) 或极性反转 180° (1’b1)。

- 旋转 (Rotation):旋转的方向和角度(采用 [R2,R1,R0] 的 二进制补码形式):

- -1 至 -4 表示 -40° 到 -160° 旋转

- 0 至 3 表示 +40° 到 +160° 旋转

- 翻转 (Flip, msb):导致下一个状态发生 180° 变化 (1’b1),忽略旋转和极性。

符号信息在两个连续线态之间的转换中捕获,如图 13所示,其中来自映射器的 5’b01011 编码符号表示从当前状态 WS02 转换到下一个状态 WS05。其中映射函数排除符号:’0’、’7’、’9’、’E’(对应相位图中±20°与±40°旋转,易引入时序噪声),并排除翻转符号:’G’(180°旋转或Flip参数触发,因冗余被剔除),此优化将符号数据从45比特压缩至36比特,简化硬件实现。

图 14 说明了用于 18 线态模式的新映射和编解码功能。

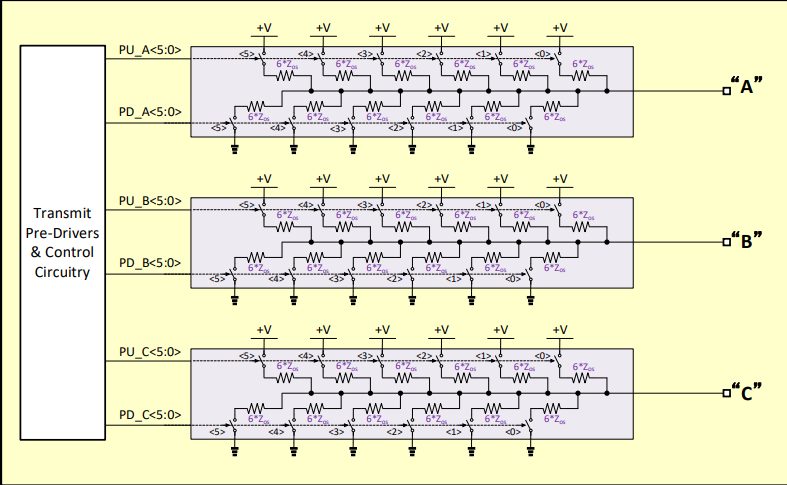

从电气角度看,三线组中的每条线被驱动到七个等距的电平之一:LSL0 到 LSL6。在任何给定时刻,所有线都处于不同的电平,确保所有差分接收器上都有非零电压,并且无论传输的线状态(WS00 到 WS17)如何,都保持相同的共模电压。

如图15所示,18 线态线路驱动器是 6 线态驱动器的扩展,包含六个由预驱动器电路单独控制的上拉/下拉支路。每个支路的输出阻抗是标称差分阻抗的六倍,并且可以轻松生成 6 线态模式所需的“高”、“低”和“中”电平,无需在 18 线态模式中使用发射器去加重。

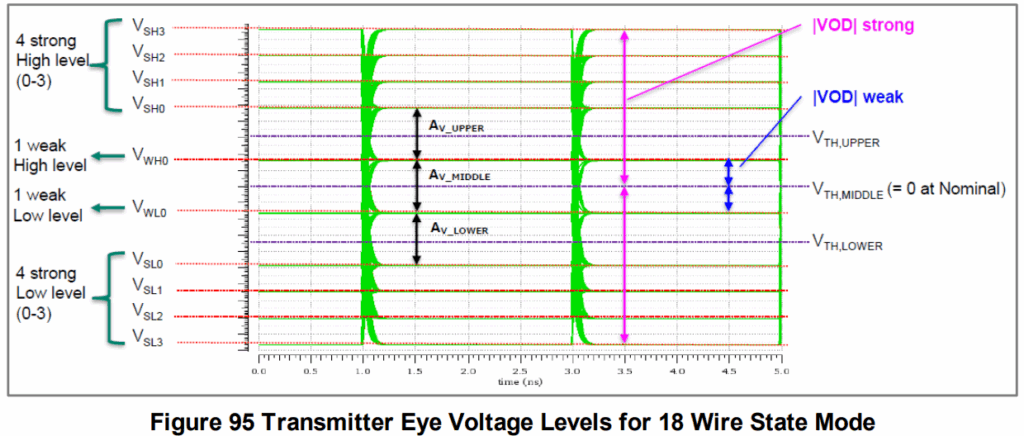

现有设计中每个接收器能够检测十个差分电平:四个强高电平、一个弱高电平、四个强低电平和一个弱低电平,此外还有三个相关的眼图(上、中、下),如图 16 所示。由于电平数量的增加,发射端功耗必然提升,目前18线态模式下最高的差分输出电压摆幅(VOD)约为6线态模式的两倍。

如图17所示,尽管存在多种信号电平,但每个接收器只需要区分四种不同的电压范围——强高 (Strong High)、弱高 (Weak High)、弱低 (Weak Low) 和强低 (Strong Low),使用三个独立的阈值电平在垂直方向分割眼图并产生四种可能输出之一。由于多电平信号传输降低了信噪比 (SNR),新型接收器的灵敏度被设计为 6 线态模式的两倍,并且始终与CTLE 配合以补偿通道引起的码间干扰 (ISI)。

最新的 MIPI C-PHY 规范定义了 5 Gsps 的最大符号速率,当在 18 线态模式下运行时,在标准参考通道下每通道达到 5 * 3.55 = 17.75 Gbps。这远远超过了在 6 线态模式下即使以更高的 6 Gsps 符号速率运行可实现的 6 * 2.28 = 13.68 Gbps 每通道吞吐量。当考虑短参通道时,性能差距进一步扩大:18 线状态模式每通道可提供高达 7 * 3.55 = 24.84 Gbps,而在 6 线状态模式下为 8 * 2.28 = 18.24 Gbps。

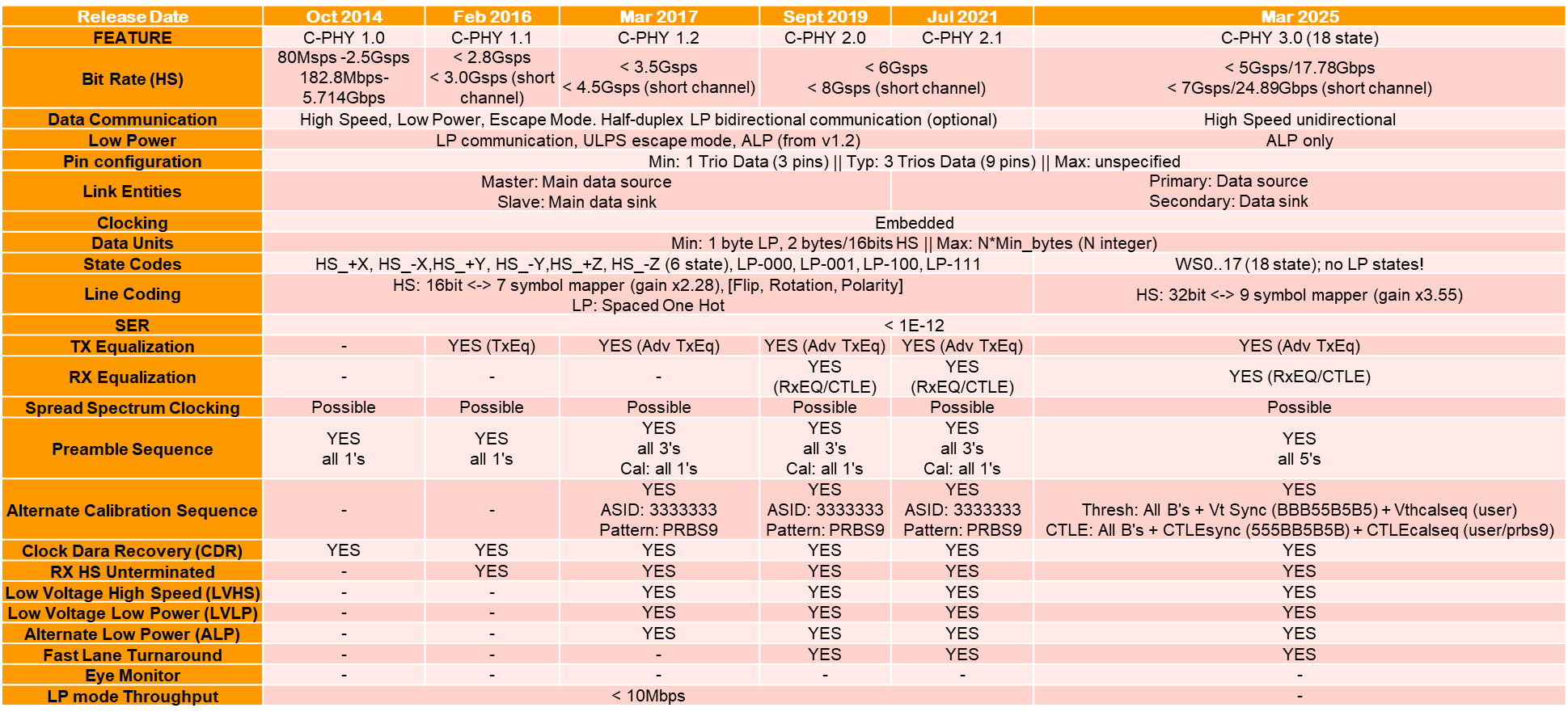

MIPI C-PHY 特性演进总结

下表总结了MIPI C-PHY各规格版本的主要特性。

结论

总之,MIPI D-PHY 和 MIPI C-PHY 技术的进步,包括 MIPI D-PHY 中的交替低功耗 (ALP) 模式、嵌入式时钟 (ECM) 模式以及 MIPI C-PHY 中的 18 线态模式等特性,有效解决兼容先进工艺节点、增加传输距离、减少线缆数量、降低 EMI 辐射以及提升数据吞吐量等关键挑战。这些创新高效利用了现有基础硬件,保证了更低的成本和更好的兼容性。随着技术的持续演进,这些接口高速性和灵活性将推动下一代高速通信系统在摄像和显示应用的发展。

MIPI® 和MIPI M-PHY®是MIPI Alliance拥有的注册商标。MIPI C-PHYTM和MIPI D-PHYTM是MIPI Alliance的商标。