For more information, contact us here.

C-PHY running at 8.0Gsps

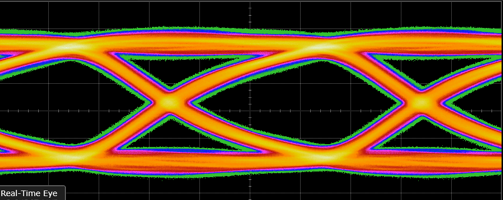

D-PHY running at 6.5Gbps

The Mixel MIPI C/D-PHY combo IP (MXL-CPHY-DPHY) is a high-frequency low-power, low cost, physical layer compliant with the MIPI® Alliance Standard for C-PHY and D-PHY. (Learn more about Mixel’s MIPI ecosystem at Mixel MIPI Central which gives you access to Mixel’s best of class MIPI ecosystem supply chain partners.)

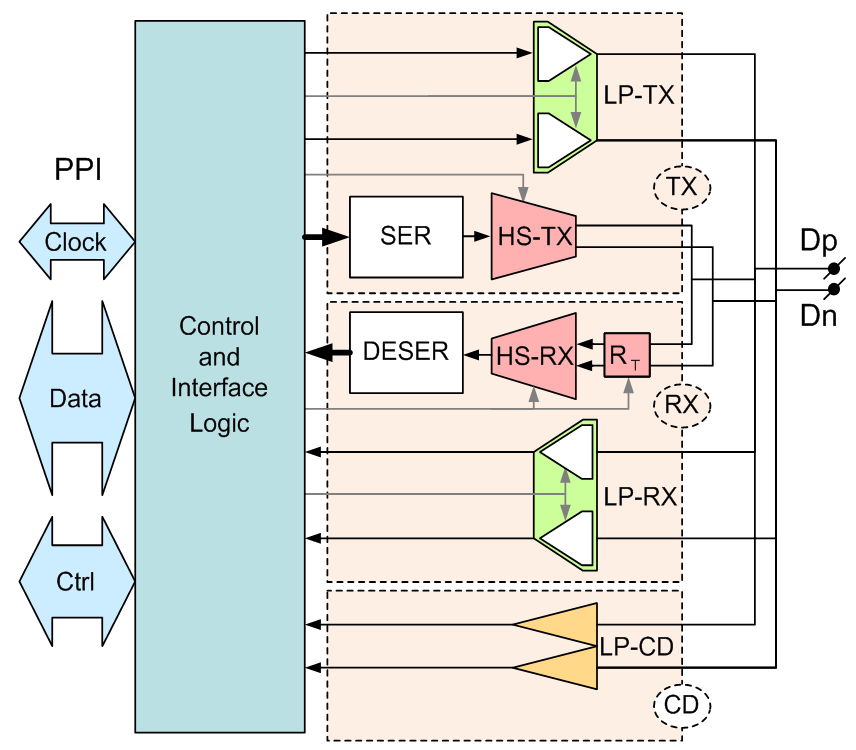

The PHY can be configured as a MIPI Primary (Master) or MIPI Secondary (Slave), supporting camera interface CSI-2 v4.0.1 or display interface DSI v2.1 applications in the D-PHY mode. It also supports camera interface CSI-2 v4.0.1 and display interface DSI-2 v2.1 applications in the C-PHY mode. The high-speed signals have a low voltage swing, while low-power signals have large swing. High-Speed functions are used for high-speed data traffic while low-power functions are mostly used for control.

The C-PHY is based on 3-Phase symbol encoding technology, delivering 2.28 bits per symbol over three-wire trios, operating with a symbol rate range of 80 to 8000 Msps per lane, which is the equivalent of about 182.8 to 18240 Mbps per lane.

The D-PHY supports a bit rate range of 80 to 1500 Mbps per Lane without deskew calibration, and up to 6500 Mbps with deskew calibration.

The low-power mode and escape mode are the same in both the D-PHY and C-PHY modes. To minimize EMI, the drivers for low-power mode are slew-rate controlled and current limited. The data rate in low-power mode is 10 Mbps. For a fixed clock frequency, the available data capacity of a PHY configuration can be increased by using more lanes. Effective data throughput can be reduced by employing burst mode communication.

Mixel’s C-PHY/D-PHY combo is a complete PHY, silicon-proven at multiple foundries and multiple nodes. The C/D-PHY is fully integrated and has analog circuitry, digital, and synthesizable logic.

The Mixel MIPI C-PHY/D-PHY Combo (MXL-CPHY-DPHY) Features:

- Dual mode PHY can support C-PHY and D-PHY

- Supports MIPI® D-PHY Specification Version 3.5 with backwards compatibility for vv3.0, v2.5, 2.1, v1.2, and v1.1

- Supports MIPI C-PHY Specification Version 2.1 with backwards compatibility for v2.0, v1.1, and v1.2

- Four lanes in D-PHY mode and three lanes in C-PHY mode

- Supports both high-speed and low-power modes

- 80 Mbps to 1.5 Gbps data rate per lane in D-PHY mode without deskew calibration

- Up to 6.5 Gbps data rate per lane in D-PHY mode with deskew calibration

- 80 Msps to 8.0 Gsps symbol rate per lane in C-PHY high-speed mode

- Equivalent to 182.8 Mbps to 18.24 Gbps per lane in C-PHY high-speed mode

- 10 Mbps data rate in low-power mode

- Low power dissipation

- Loopback testability (BIST) support

- Optional resistance termination calibrator

- Deskew calibration support in D-PHY

The Mixel MIPI C/D-PHY combo (MXL-CPHY-DPHY) has many benefits including:

- Area overhead is minimized by reusing all of the D-PHY blocks for the C-PHY operation and sharing of all the serial interface pins

- Comprehensive embedded DFT features for allowing cost-effective high-volume manufacturing tests

- Support for full-speed internal loopback testability with minimal area overhead for high-volume manufacturing tests in the C/D-PHY Universal, TX+, and RX+ configurations

In addition, the Mixel MIPI C-PHY v2.1/MIPI D-PHY v2.5 has additional benefits including:

- Support for MIPI D-PHY v2.5 and MIPI C-PHY v2.1 features not available in previous versions of the specifications such as Spread Spectrum Clocking (SSC) and transmit equalization (de-emphasis)

- Support for new power saving functionality such as HS-TX half swing mode and HS-RX unterminated mode

- Support for new Alternate LP Mode, suitable for IoT applications with long channels, enabling Fast Bus Turnaround

Mixel’s Production Ready Offering (“PRO IP”): MIPI C-PHY/D-PHY Combo IP

| C-PHY/D-PHY Combo DSI TX+ (3T/4L, 4.5Gsps/4.5Gbps) in TSMC N5 | More information |

| C-PHY/D-PHY Combo CSI RX+ (3T/4L, 4.5Gsps/4.5Gbps) in TSMC N5 | More information |

| C-PHY/D-PHY Combo CSI-2 RX+ (3T/4L, 6.0Gsps/4.5Gbps) in TSMC N6 | More information |

| C-PHY/D-PHY combo CSI-2 RX (3T/4L, 4.5Gsps/4.5Gbps) in TSMC N7 | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (3T/4L, 4.5Gsps/4.5Gbps) in TSMC 16FFC | More information |

| C-PHY/D-PHY Combo DSI RX+ (3T/4L, 4.5Gsps/6.5Gbps) in TSMC 16FFC | More information |

| C-PHY/D-PHY Combo Universal (3T/4L, 8.0Gsps/6.5Gbps) in TSMC 16FFC | More information |

| C-PHY/D-PHY Combo DSI RX (3T/4L, 2.5Gsps/2.5Gbps) in TSMC 22ULP | More information |

| C-PHY/D-PHY Combo CSI-2 TX (3T/4L, 2.5Gsps/2.5Gbps) in TSMC 22ULL | More information |

| C-PHY/D-PHY Combo CSI-2 TX (3T/4L, 4.5Gsps/4.5Gbps) in TSMC 28HPC+ | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (3T/4L, 3.5Gsps/2.5Gbps) in ST 28FDSOI | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (3T/4L, 3.5Gsps/2.5Gbps) in STM 40LP | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (2T/2L, 3.5Gsps/2.5Gbps) in STM 40LP | More information |

| C-PHY/D-PHY Combo CSI-2 TX (2T/2L, 1.5Gsps/1.5Gbps) in TSMC 40ULP | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (1T/1L, 2.5Gsps/2.5Gbps) in TSMC 40ULP | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (2T/2L, 2.5Gsps/2.5Gbps) in TSMC 40ULP | More information |

| C-PHY/D-PHY Combo CSI-2 TX+ (1L/1T, 1.5Gsps/1.5Gbps) in TSMC 65LP | More information |