Mixed-Signal Excellence

## MXL-CDPHY-CSITX-T-28HPCP

## **1** Features

- Dual mode PHY Supports MIPI Alliance Specification D-PHY v2.5 & C-PHY v2.0

- Consists of 1 Clock lane and 4 Data lanes in D-PHY mode

- Consists of 3 Data lanes in C-PHY mode

- Embedded, high performance, and highly programmable PLL

- PLL supports SSC mode, Fractional mode, and Integer mode

- Supports both low-power mode and high speed mode with integrated SERDES

- 80 Mbps to 1.5 Gbps data rate per lane without skew calibration in D-PHY mode

- 3.5 Gbps data rate per lane with skew calibration in high speed D-PHY mode

- 80 Msps to 3.5 Gsps symbol rate per lane in high speed C-PHY mode

- Supports High Speed TX De-emphasis Equalization

- 10 Mbps data rate in low-power mode

- Low power dissipation

- Testability support

- Calibrator for resistance termination

## 2 General Description

The MXL-CD-PHY-CSITX-T-28HPCP is a high-frequency, low-power, low-cost, sourcesynchronous, physical Layer supporting the MIPI Alliance Specification for D-PHY v2.5 and C-PHY v2.0. The PHY can be configured as a MIPI Master supporting camera interface CSI-2. The PHY supports mobile, IoT, virtual reality, and automotive applications.

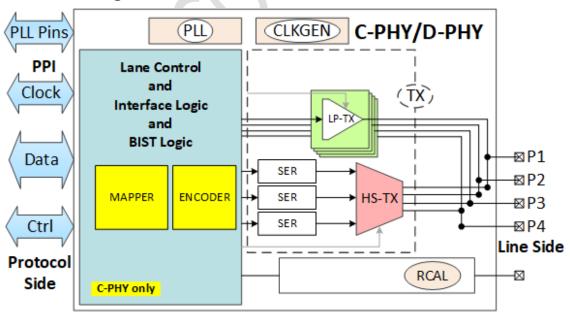

## 3 Block Diagram

Figure 3-1: MIPI CD-PHY Block Diagram

Subject to change Without notice Proprietary & Confidential

Mixel, Inc. 97 East Brokaw, San Jose, CA 95112 Ph.: (408) 436-8500, Fax: (408) 436-8400 www.mixel.com P. 3 of 113 Rev 0.1