## Mixed-Signal Excellence

### **Features:**

- 25-180 MHz clock support

- Up to 1.25 Gbps bandwidth

- Up to 5.0 Gbps data throughput

- Low power CMOS design

- Power Down mode

- Low swing LVDS devices for low EMI

- PLL requires no external components

- 1.8V/3.3V dual power supply

- 7/10 bit programmable parallel data transmitted per pixel clock per cannel

- Compatible with TIA/EIA-644 LVDS Standard

# Four Channel LVDS De-serializer IP

#### MXL-LVDS-DS-4CH

## **General Description:**

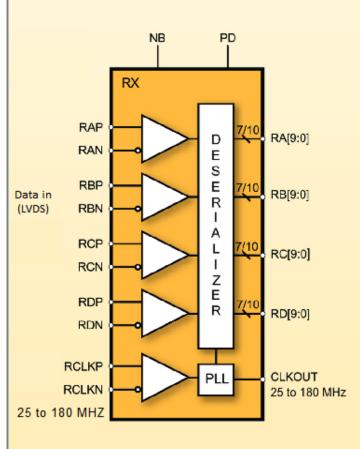

The MXL-LVDS-RX-4CH is a high performance 4-channel LVDS De-serializer implemented using digital CMOS technology. Both the serial and parallel data are organized into four channels. The parallel data can be 7 or 10 bits wide per channel. The input clock is 25MHz to 180MHz. The Receiver is highly integrated and requires no external components. Great care was taken to insure matching between the Data and Clock channels to maximize the receiver margin. The circuit is designed in a modular fashion and desensitized to process variations. This facilitates process migration, and results in a robust design.

Preliminary information Subject to change Without notice Mixel, Inc. 4423 Fortran Court, San Jose, CA 95134 Ph.: (408) 942-9300, Fax: (408) 942-9700 www.mixel.com

## **Block Diagram:**